1 receive fifo service (rfs), 2 receive packet complete (rpc), 3 receive overflow (rof) – Intel PXA255 User Manual

Page 433: Udccs4/9/14 bit definitions -33

Intel® PXA255 Processor Developer’s Manual

12-33

USB Device Controller

12.6.7.1

Receive FIFO Service (RFS)

The receive FIFO service bit is set if the receive FIFO has one complete data packet in it and the

packet has been error checked by the UDC. A complete packet may be 256 bytes, a short packet, or

a zero packet. UDCCSx[RFS] is not cleared until all data is read from both buffers.

12.6.7.2

Receive Packet Complete (RPC)

The receive packet complete bit gets set by the UDC when an OUT packet is received. When this

bit is set, the IRx bit in the appropriate UDC status/interrupt register is set if receive interrupts are

enabled. This bit can be used to validate the other status/error bits in the endpoint(x) control/status

register. The UDCCSx[RPC] bit is cleared by writing a 1 to it.

12.6.7.3

Receive Overflow (ROF)

The receive overflow bit generates an interrupt on IRx in the appropriate UDC status/interrupt

register to alert the software that Isochronous data packets are being dropped because neither FIFO

buffer has room for them. This bit is cleared by writing a 1 to it.

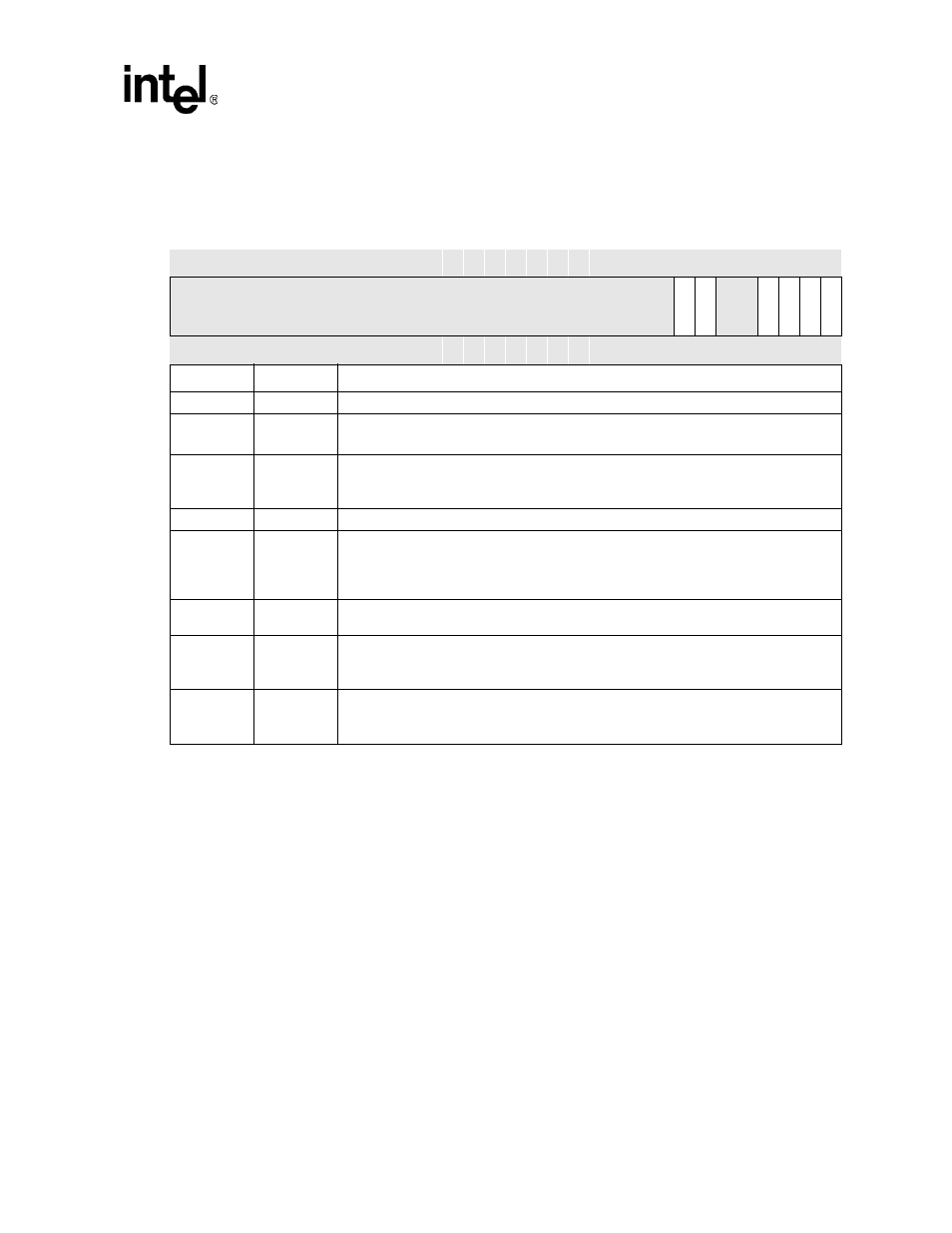

Table 12-18. UDCCS4/9/14 Bit Definitions

0x 4060_0020

0x 4060_0034

0x4060_0048

UDCCS4

UDCCS9

UDCCS14

USB Device Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

RS

P

RN

E

reser

ved

DM

E

RO

F

RP

C

RF

S

Reset

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

0

0

0

0

0

0

Bits

Name

Description

31:8

—

reserved

7

RSP

Receive short packet (read-only)

0 = Short packet received and ready for reading.

6

RNE

Receive FIFO not empty (read-only).

0 = Receive FIFO empty.

1 = Receive FIFO not empty.

5:4

—

reserved

3

DME

DMA Enable(read/write)

0 = Send receive interrupt after EOP receive

1 = Send data received interrupt after EOP received and Receive FIFO has < 32 bytes of

data

2

ROF

Receive overflow (read/write 1 to clear)

1 = Isochronous data packets are being dropped from the host because the receiver is full.

1

RPC

Receive packet complete (read/write 1 to clear).

0 = Error/status bits invalid.

1 = Receive packet has been received and error/status bits are valid.

0

RFS

Receive FIFO service (read-only).

0 = Receive FIFO has less than 1 data packet.

1 = Receive FIFO has 1 or more data packets.