Lcsr bit definitions -40 – Intel PXA255 User Manual

Page 302

7-40

Intel® PXA255 Processor Developer’s Manual

LCD Controller

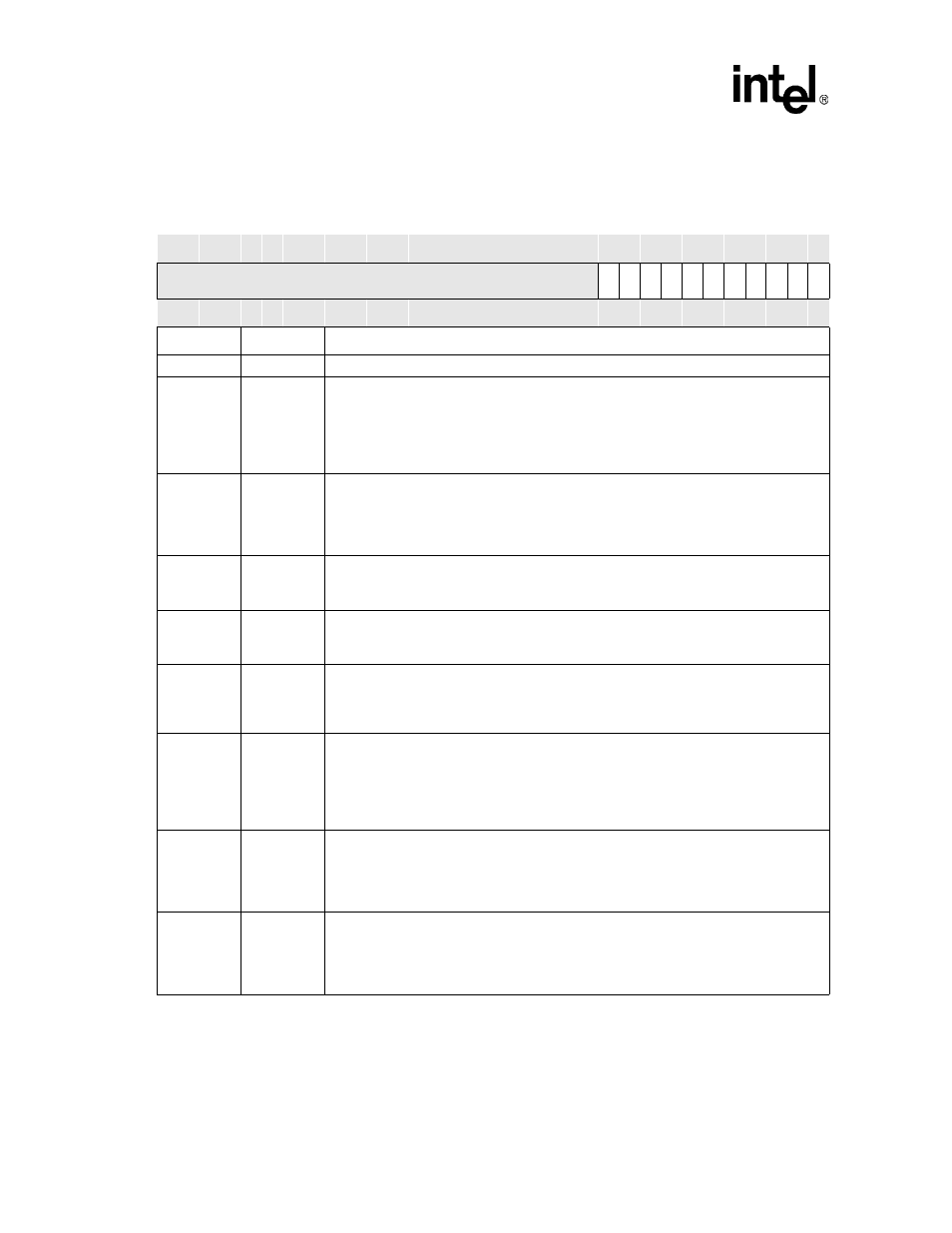

Table 7-12. LCSR Bit Definitions (Sheet 1 of 2)

Physical Address

0x4400_0038

LCD Controller Status Register 1

LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

SIN

T

BS

EO

F

QD

OU

IU

U

IU

L

AB

C

BE

R

SO

F

LD

D

Reset

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:11

—

reserved

10

SINT

Subsequent Interrupt status, maskable interrupt:

0 = A second unmasked branch, start of frame, end of frame, or bus error interrupt has

NOT occurred before a previous interrupt has completed.

1 = A second unmasked branch, start of frame, end of frame, or bus error interrupt has

occurred before the previous interrupt has been cleared. The value in the Interrupt

Frame ID Register is not replaced with the value from the second interrupt.

9

BS

Branch Status, maskable interrupt:

0 = The DMA has not loaded a branched-to descriptor, or the DMA has loaded a

branched-to descriptor, but the branch interrupt (BINT) bit is not set in the Frame

Branch Register.

1 = The DMA has loaded a branched-to descriptor, and the BINT bit is set.

8

EOF

End Of Frame status, maskable interrupt:

0 = A new frame with the EOFINT bit set in its descriptor has not been processed.

1 = The DMA has finished fetching a frame with the EOFINT bit set in its descriptor.

7

QD

LCD Quick Disable status, maskable interrupt:

0 = LCD has not been quickly disabled by clearing LCCCR0[ENB].

1 = LCD has been quickly disabled.

6

OU

Output FIFO Underrun status, maskable interrupt:

0 = Output FIFOs have not underrun.

1 = LCD dither logic is not supplying data to output FIFOs for the panel at a sufficient rate.

The output FIFOs have completely emptied.

5

IUU

Input FIFO Underrun Upper panel status, maskable interrupt:

0 = The input FIFO for the upper (dual-panel mode) or whole panel (single-panel mode)

display has not underrun.

1 = DMA is not supplying data to the input FIFO for the upper or whole panel at a sufficient

rate. The FIFO has completely emptied, and the pixel unpacking logic has attempted

to take data from the FIFO.

4

IUL

Input FIFO Underrun Lower panel status, dual-panel mode only, maskable interrupt:

0 = The input FIFO for the lower panel display has not underrun.

1 = DMA is not supplying data to the input FIFO for the lower panel at a sufficient rate. The

FIFO has completely emptied, and the pixel unpacking logic has attempted to take

data from the FIFO.

3

ABC

AC Bias Count status, nonmaskable interrupt:

0 = The AC bias transition counter has not decremented to zero.

1 = The AC bias transition counter has decremented to zero, indicating that the L_BIAS

pin has toggled the number of times specified by the LCCR3[API] control-bit field. The

counter is reloaded with the value in API but is disabled until the user clears ABC.