Table 6-15 – Intel PXA255 User Manual

Page 219

Intel® PXA255 Processor Developer’s Manual

6-37

Memory Controller

6.6.2

Synchronous Static Memory Mode Register Set

Configuration Register (SXMRS)

On power up, a MRS command that contains the default boot-up value is written to the external

memory if the system is configured to boot out of SMROM (see

). Otherwise,

SXMRS, shown in

, is used to issue an MRS command to SMROM. The value written

in this register is placed directly on address lines MA<24:10> during the MRS command. Writing

to this register triggers a two-stage MRS command that is sent to the external synchronous static

memory. The first state issues an MRS command to banks 0 and 1. The second stage issues an

MRS command to banks 2 and 3. The corresponding chip select values are only asserted if the

memory banks are enabled via the SXCNFG register and the memory type is configured as

SMROM.

To write a new MRS value to a synchronous static memory, first enable and configure the memory

via the SXCNFG register, then write the SXMRS register. This register is only used for the value

written during the MRS command. All values in the SXCNFG register must be programmed

correctly to ensure proper device operation (refer to the external memory chip product

documentation for proper MRS encoding). Information programmed in the SXCNFG[CL] and

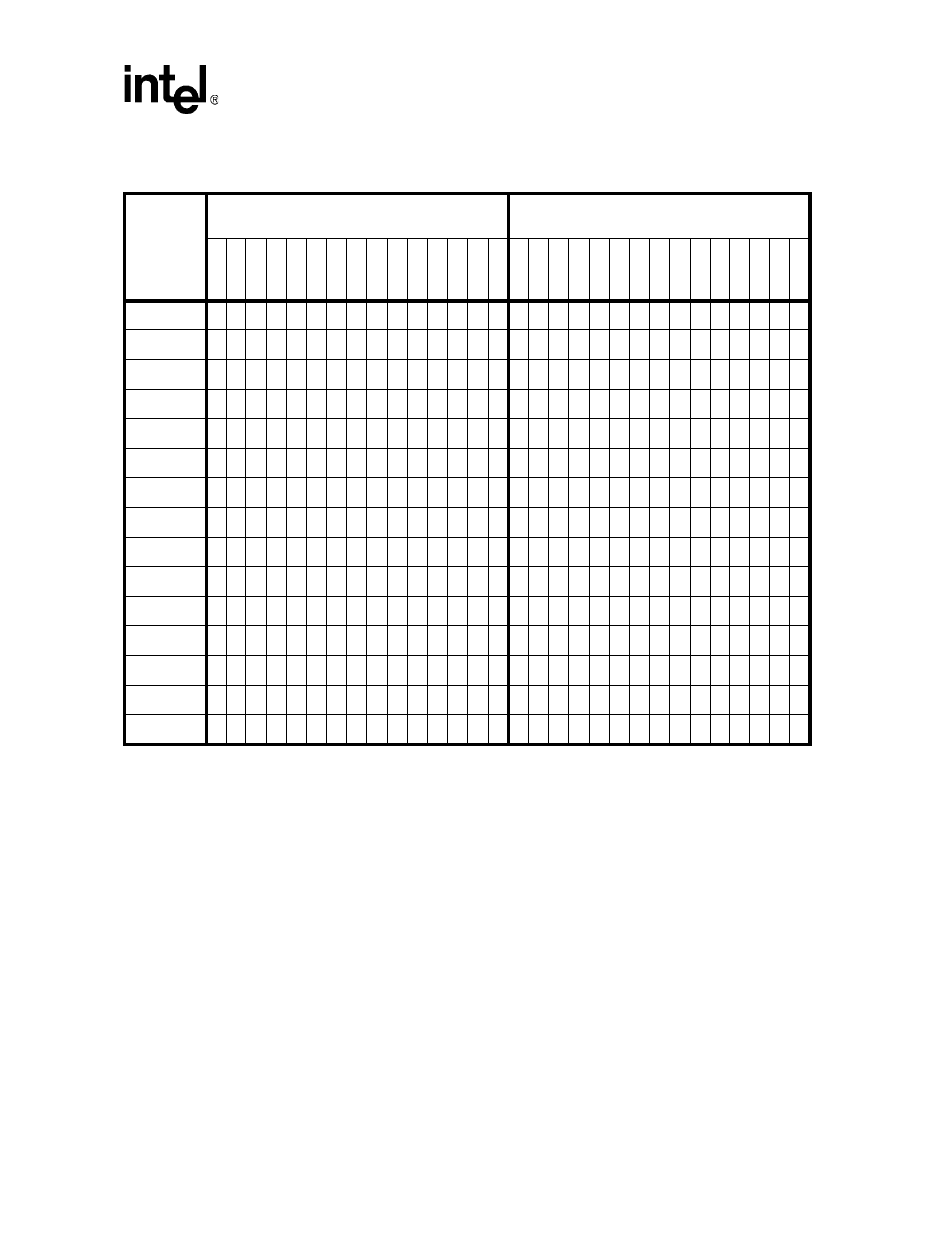

Table 6-15. Synchronous Static Memory External to Internal Address Mapping Options

# Bits

Bank x

Row x

Col x

Data

External Address pins at SXMEM RAS Time

MA<24:10>

External Address pins at SXMEM CAS Time

MA<24:10>

24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

2x12x7x32

22 21 20 19 18 17 16 15 14 13 12 11 10

9

22 21

0

8

7

6

5

4

3

2

2x12x7x16

21 20 19 18 17 16 15 14 13 12 11 10

9

8

21 20

0

7

6

5

4

3

2

1

2x12x8x32

23 22 21 20 19 18 17 16 15 14 13 12 11 10

23 22

0

9

8

7

6

5

4

3

2

2x12x8x16

22 21 20 19 18 17 16 15 14 13 12 11 10

9

22 21

0

8

7

6

5

4

3

2

1

2x12x9x32

24 23 22 21 20 19 18 17 16 15 14 13 12 11

24 23

0

10

9

8

7

6

5

4

3

2

2x12x9x16

23 22 21 20 19 18 17 16 15 14 13 12 11 10

23 22

0

9

8

7

6

5

4

3

2

1

2x12x10x32

25 24 23 22 21 20 19 18 17 16 15 14 13 12

25 24

0

11 10

9

8

7

6

5

4

3

2

2x12x10x16

24 23 22 21 20 19 18 17 16 15 14 13 12 11

24 23

0

10

9

8

7

6

5

4

3

2

1

2x13x7x32

23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

23 22

0

8

7

6

5

4

3

2

2x13x7x16

22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

22 21

0

7

6

5

4

3

2

1

2x13x8x32

24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 24 23

0

9

8

7

6

5

4

3

2

2x13x8x16

23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

23 22

0

8

7

6

5

4

3

2

1

2x13x9x32

25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 25 24

0

10

9

8

7

6

5

4

3

2

2x13x9x16

24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 24 23

0

9

8

7

6

5

4

3

2

1

2x13x10x16

25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 25 24

0

10

9

8

7

6

5

4

3

2

1