Gafr2_l bit definitions -19, Gafr2_u bit definitions -19, Table 4-28 – Intel PXA255 User Manual

Page 123: Table 4-29

Intel® PXA255 Processor Developer’s Manual

4-19

System Integration Unit

4.1.3.7

Example Procedure for Configuring the Alternate Function Registers

In this example, GP0 is used as a generic GPIO and GP[15:1] are configured as their alternate

functions. Refer to

for the list of alternate functions. No other GPIOs are configured.

After the de-assertion of any RESET, GPDR0[15:0] configures GPIO pins in this example to be

inputs. GAFR00[31:0] will be 0x0000_ 0000 to indicate normal GPIO function. For simplicity,

assume that GP[16-31] are inputs configured as normal GPIOs.

In this example,

•

GPIO[0] is configured as a normal GPIO input

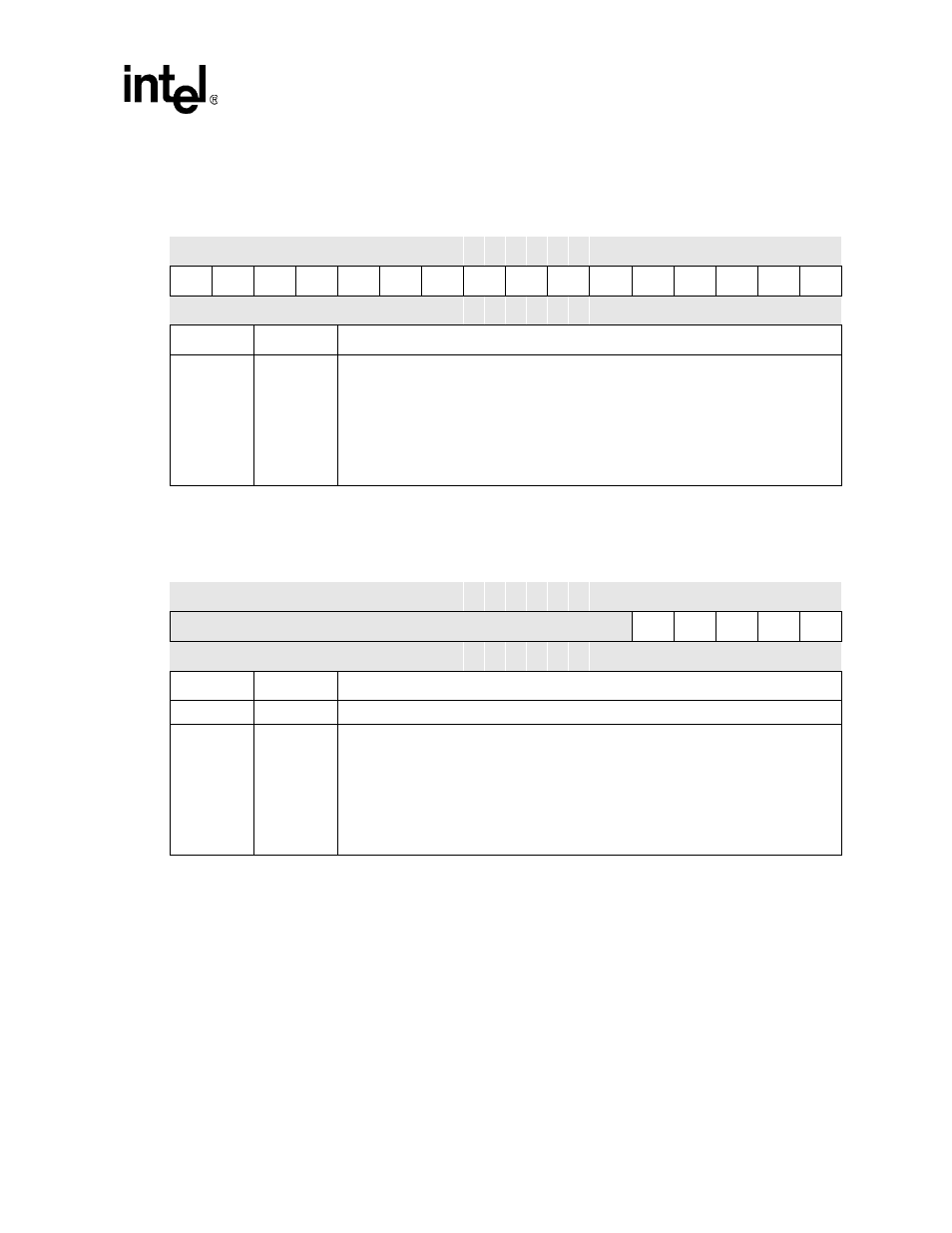

Table 4-28. GAFR2_L Bit Definitions

Physical Address

0x40E0_0064

GAFR2_L

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

AF79

AF78

AF77

AF76

AF75

AF74

AF73

AF72

AF71

AF70

AF69

AF68

AF67

AF66

AF65

AF64

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:0>

AF[x]

GPIO Pin ‘x’ Alternate Function Select Bits (where x=64 through 79).

A bit-pair in this register determines the corresponding GPIO pin’s functionality as one of

the alternate functions that is mapped to it or as a generic GPIO pin.

00 – The corresponding GPIO pin (GPIO[x]) is used as a general purpose I/O.

01 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 1.

10 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 2.

11 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 3.

Table 4-29. GAFR2_U Bit Definitions

Physical Address

0x40E0_0068

GAFR2_U

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

AF84

AF83

AF82

AF81

AF80

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:10>

—

reserved

<9:0>

AF[x]

GPIO Pin ‘x’ Alternate Function Select Bits (where x=80 through 84).

A bit-pair in this register determines the corresponding GPIO pin’s functionality as one of

the alternate functions that is mapped to it or as a generic GPIO pin.

00 – The corresponding GPIO pin (GPIO[x]) is used as a general purpose I/O.

01 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 1.

10 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 2.

11 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 3.