Alternate bus master mode -69, Variable latency io -69, Figure 6-31 – Intel PXA255 User Manual

Page 251: Figure 6-32

Intel® PXA255 Processor Developer’s Manual

6-69

Memory Controller

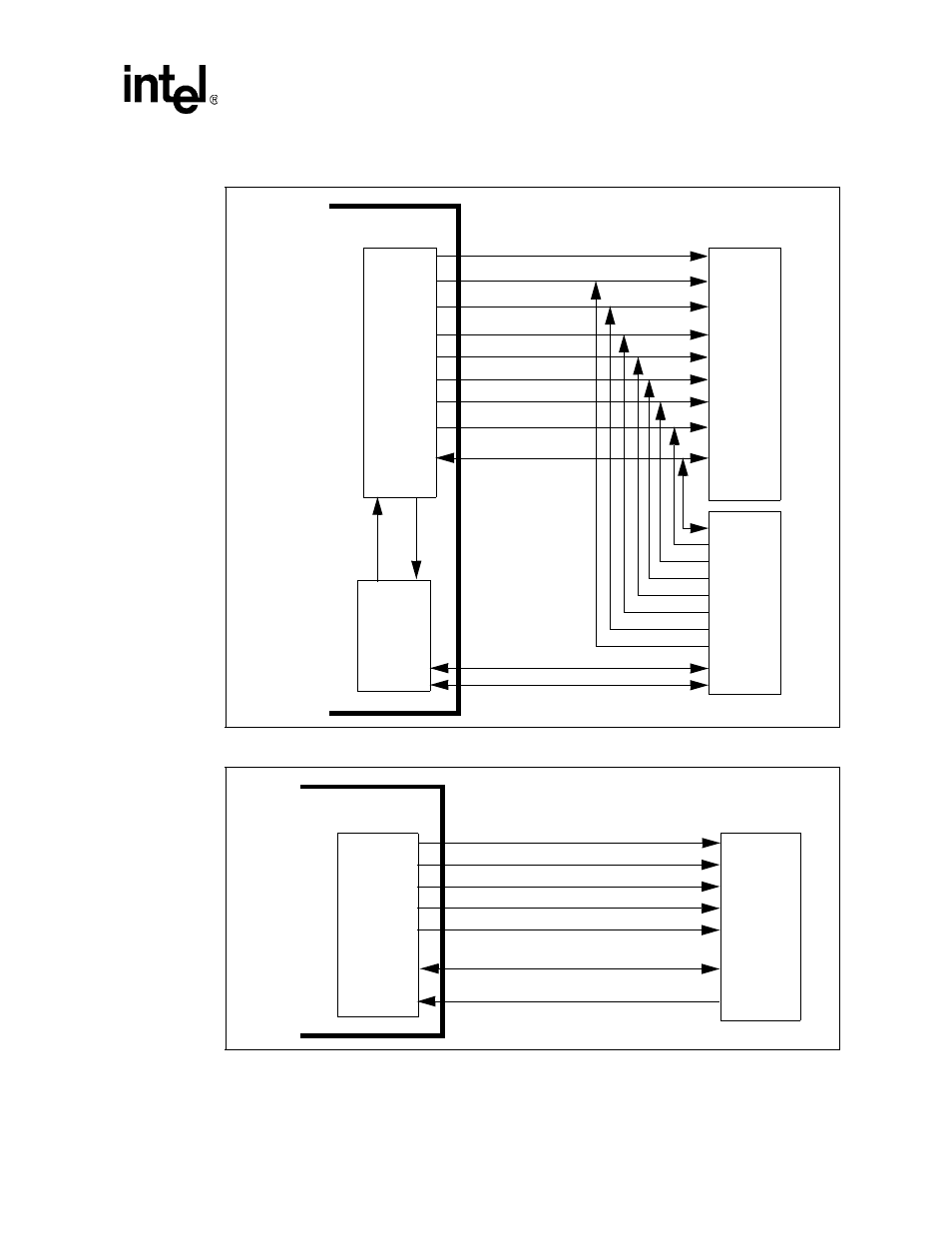

Figure 6-31. Alternate Bus Master Mode

Figure 6-32. Variable Latency IO

Processor

EXTERNAL SYSTEM

MB

REQ

MBG

N

T

GPIO<13> (MBGNT)

GPIO<14> (MBREQ)

nSDCS(0)

nWE

nSDRAS

nSDCAS

MD[31:0]

MA[25:0]

SDCLK<1>

DQM[3:0]

SDCKE<1>

Memory

Controlle

External

SDRAM

Bank 0

Companion

Chip

GPIO

Block

Processor

EXTERNAL SYSTEM

nCS(0,1,2,3,4,5)

nPWE

nOE

RDY

MD[31:0]

MA[25:0]

DQM[3:0]

Companion

Chip

Memory

Controller