Cpu core fault register bit definitions -3 – Intel PXA255 User Manual

Page 33

Intel® PXA255 Processor Developer’s Manual

2-3

System Architecture

2.2.2

Coprocessor 14 Registers 0-3 - Performance Monitoring

The processor does not define any performance monitoring features beyond those called out in the

Intel® XScale™ Microarchitecture for the Intel® PXA255 Processor User’s Manual, order number

278793. The interrupt generated by performance monitoring events is defined in

Chapter 4,

“System Integration Unit”

. The ASSP defined performance monitoring events (events 0x10 -

0x17), defined through the PMNC register are reserved for the processor.

2.2.3

Coprocessor 14 Register 6 and 7- Clock and Power

Management

These registers allow software to use the clocking and power management modes. The valid

operations are described in

Table 3-23, “Coprocessor 14 Clock and Power Management Summary”

on page 3-39

.

2.2.4

Coprocessor 15 Register 0 - ID Register Definition

This register may be read by software to determine the device type and revision. The contents of

this register for the Intel® PXA255 Processor is defined in the table below. Combined, this register

must read as 0x6905 2X0R where R = 0b0000 for the first stepping and then increments for

subsequent steppings, and X is the revision of the Intel® XScale™ microarchitecture present.

Please see the Intel Developer Homepage at http://developer.intel.com for updates.

This is a read-only register.

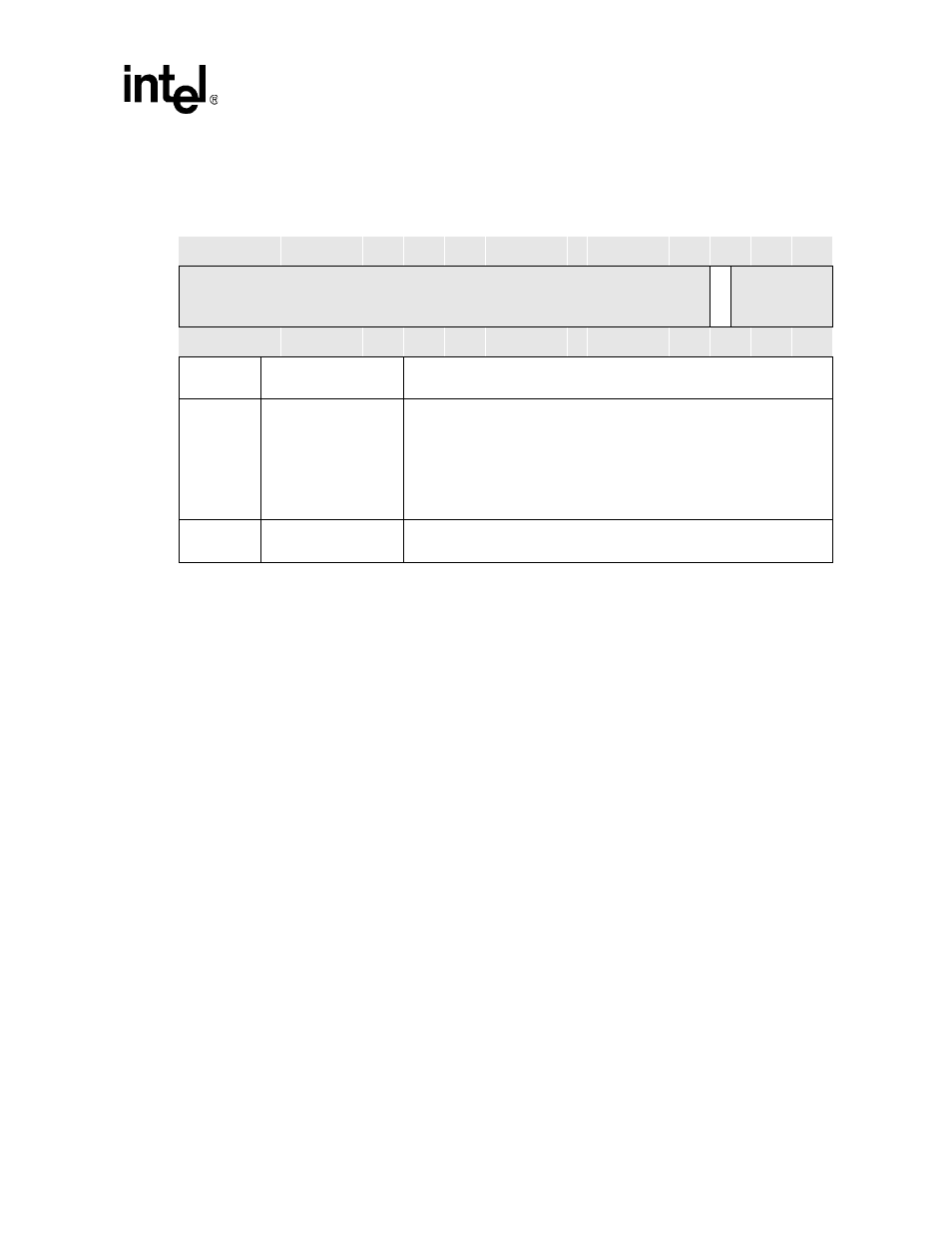

Table 2-1. CPU Core Fault Register Bit Definitions

Coprocessor 7

Register 4

CPU Core Fault

System Architecture

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Re

s

e

rv

e

d

PS

F

S

Re

s

e

rv

e

d

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

[31:6]

—

Reserved.

Read undefined.

5

PSFS

Power Source Fault Status

0 = nVDD_FAULT or nBATT_FAULT pin has not been asserted since it was

last cleared by a reset or the CPU.

1 = nVDD_FAULT or nBATT_FAULT pin was asserted and PMCR[IDAE] =

1.

Read only, write ignored.

Cleared by Hardware, Watchdog, and GPIO Resets.

[4:0]

—

Reserved.

Read undefined.