4 programmable serial protocol, Figure 16-14 – Intel PXA255 User Manual

Page 555

Intel® PXA255 Processor Developer’s Manual

16-15

Network SSP Serial Port

Note:

SSCR1[TTELP] must be 0 for National Semiconductor Microwire.

16.4.4.4

Programmable Serial Protocol

When SSCR1[TTE] is 0, the SSP behaves as described in

If SSCR1[TTE] is 1 and SSCR1[TTELP] is 0, SSPTXD is driven at the same clock edge that the

MSB is driven. If the SSP is a slave to frame SSPTXD is Hi-Z on the clock edge after the edge that

starts the LSB.

shows the pin timing for this mode.

If the SSP is a master to frame, SSPTXD is Hi-Z two clock edges after the clock edge that drives

the LSB. This occurs even if the SSP is a master of clock and this clock edge does not appear on

the SSPSCLK.

shows the pin timing for this mode.

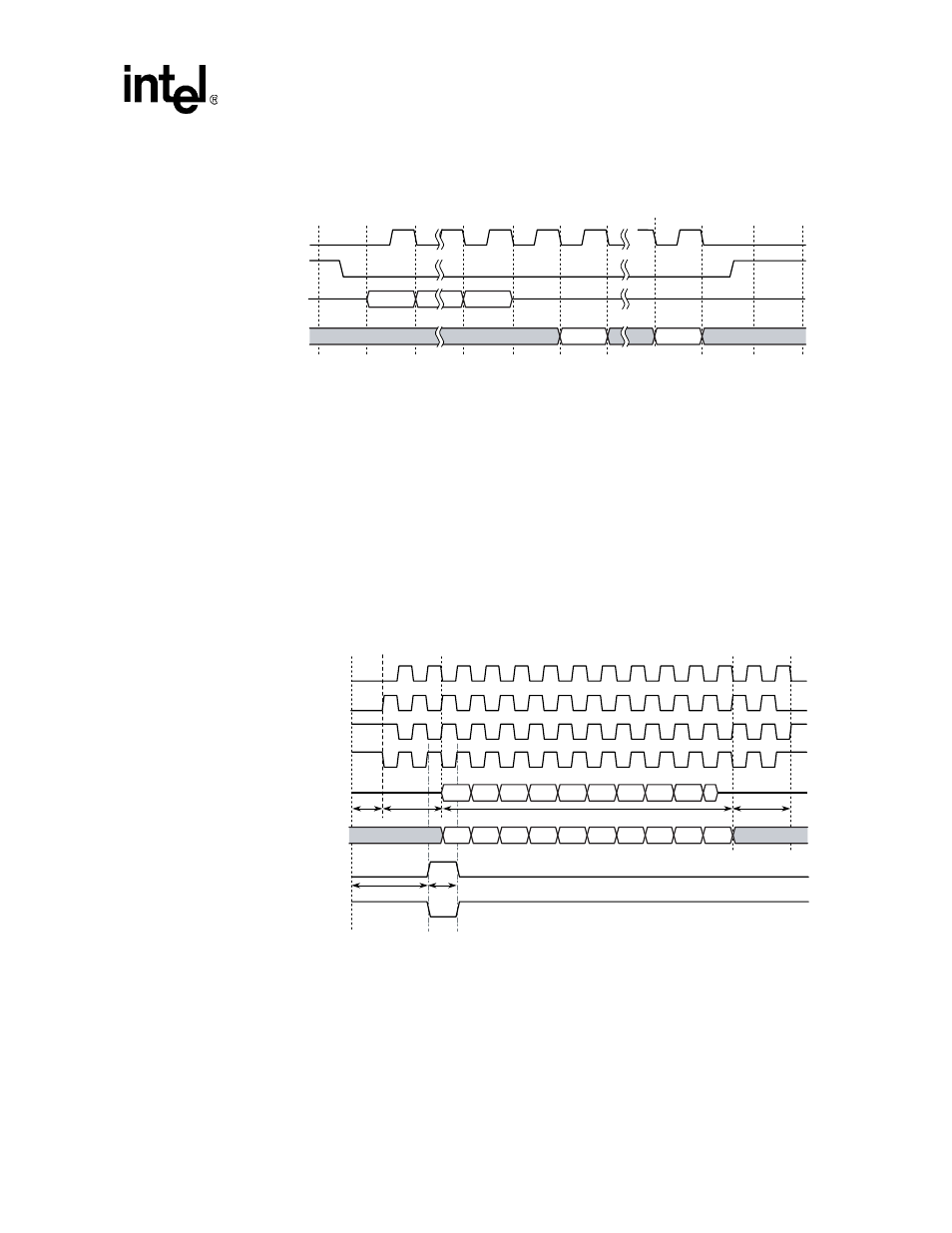

Figure 16-14. National Semiconductor Microwire with SSCR1[TTE]=1

A9977-01

SSPRXD

SSPSFRM

SSPSCLK

SSPTXD

4 to 32 Bits

Bit[7] or

Bit[15]

8 or 16-Bit Control

Bit[0]

Bit[N]

Bit[0]

Undefined

Undefined

Undefined

Figure 16-15. PSP mode with SSCR1[TTE]=1 and SSCR1[TTELP]=0 (slave to frame)

A9978-01

MSB

Undefined

Undefined

T1

T2

T3

T4

LSB

MSB

LSB

T6

T5

SSPSCLK

(when SCMODE = 0)

SSPSCLK

(when SCMODE = 1)

SSPSCLK

(when SCMODE = 2)

SSPSCLK

(when SCMODE = 3)

SSPSFRM

(when SFRMP = 1)

SSPSFRM

(when SFRMP = 0)

SSPTXD

SSPRXD