Gfer0 bit definitions -14, Gfer1 bit definitions -14, Gfer2 bit definitions -14 – Intel PXA255 User Manual

Page 118: Table 4-18, Table 4-20

4-14

Intel® PXA255 Processor Developer’s Manual

System Integration Unit

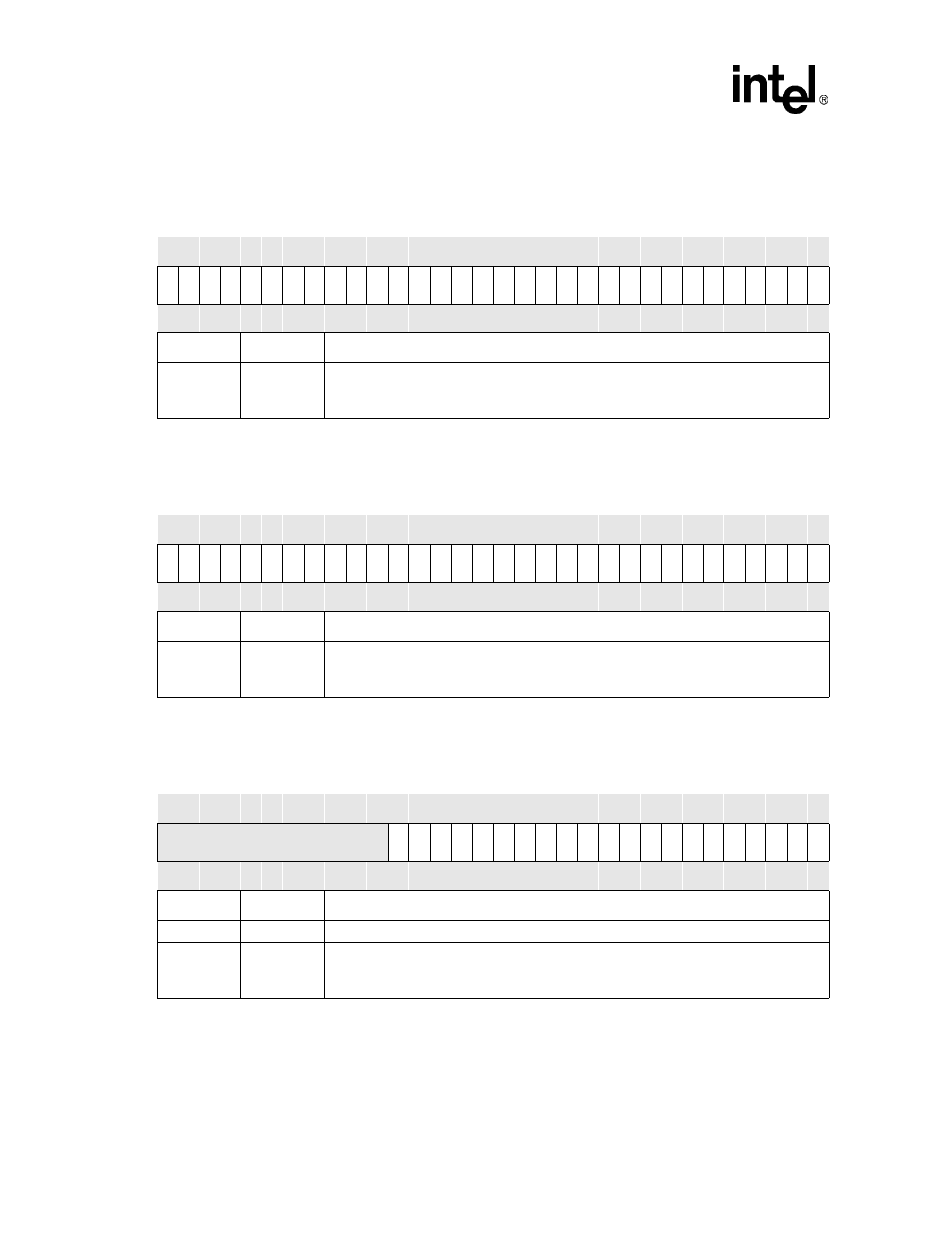

Table 4-18. GFER0 Bit Definitions

Physical Address

0x40E0_003C

GFER0

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

FE31

FE30

FE29

FE28

FE27

FE26

FE25

FE24

FE23

FE22

FE21

FE20

FE19

FE18

FE17

FE16

FE15

FE14

FE13

FE12

FE1

1

FE10

FE9

FE8

FE7

FE6

FE5

FE4

FE3

FE2

FE1

FE0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:0>

FE[x]

GPIO Pin ‘x’ Falling Edge Detect Enable (where x = 0 through 31).

0 – Disable falling-edge detect enable.

1 – Set corresponding GEDR status bit when a falling edge is detected on the GPIO pin

Table 4-19. GFER1 Bit Definitions

Physical Address

0x40E0_0040

GFER1

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

FE63

FE62

FE61

FE60

FE59

FE58

FE57

FE56

FE55

FE54

FE53

FE52

FE51

FE50

FE49

FE48

FE47

FE46

FE45

FE44

FE43

FE42

FE41

FE40

FE39

FE38

FE37

FE36

FE35

FE34

FE33

FE32

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:0>

FE[x]

GPIO Pin ‘x’ Falling Edge Detect Enable (where x = 32 through 63).

0 – Disable falling-edge detect enable.

1 – Set corresponding GEDR status bit when a falling edge is detected on the GPIO pin

Table 4-20. GFER2 Bit Definitions

Physical Address

0x40E0_0044

GFER2

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

FE

8

4

FE

8

3

FE

8

2

FE

8

1

FE

8

0

FE

7

9

FE

7

8

FE

7

7

FE

7

6

FE

7

5

FE

7

4

FE

7

3

FE

7

2

FE

7

1

FE

7

0

FE

6

9

FE

6

8

FE

6

7

FE

6

6

FE

6

5

FE

6

4

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:21>

—

reserved

<20:0>

FE[x]

GPIO Pin ‘x’ Falling Edge Detect Enable (where x = 64 through 80).

0 – Disable falling-edge detect enable.

1 – Set corresponding GEDR status bit when a falling edge is detected on the GPIO pin