Interrupt identification register decode -11 – Intel PXA255 User Manual

Page 367

Intel® PXA255 Processor Developer’s Manual

10-11

UARTs

3

TOD

(IID3)

Character Timeout Indication Detected:

0 – No Character Timeout Indication interrupt is pending

1 – Character Timeout Indication interrupt is pending (FIFO mode only)

2:1

IID[2:1]

Interrupt Source Encoded:

00 – Modem Status (CTS, DSR, RI, DCD modem signals changed state)

01 – Transmit FIFO request data

10 – Received Data Available

11 – Receive error (Overrun, parity, framing, break, FIFO error)

0

IP

Interrupt Pending:

0 – Interrupt is pending (Active low)

1 – No interrupt is pending

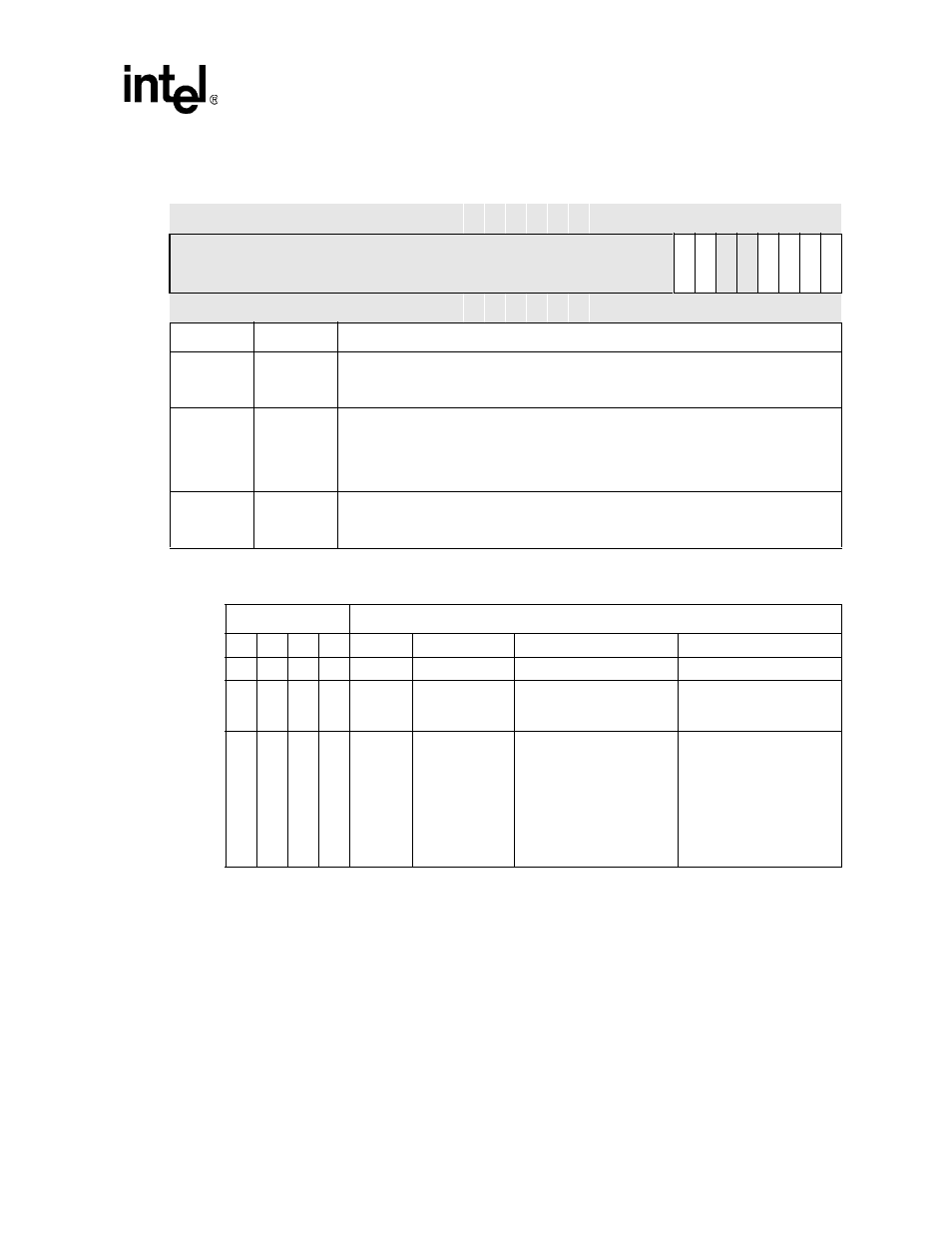

Table 10-10. Interrupt Identification Register Decode (Sheet 1 of 2)

Interrupt ID Bits

Interrupt SET/RESET Function

3

2

1

0

Priority

Type

Source

Cleared By...

0

0

0

1

—

None

No interrupt is pending

—

0

1

1

0

Highest

Receiver Line

Status

Overrun error, parity error,

framing error, break

interrupt

Reading the LSR

0

1

0

0

Second

Highest

Received Data

Available

Non-FIFO mode: Receive

buffer is full

FIFO mode: Trigger level

was reached

Non-FIFO mode: Reading

the Receiver Buffer

Register

FIFO mode: Reading bytes

until Receiver FIFO drops

below trigger level or setting

FCR[RESETRF].

Table 10-9. IIR Bit Definitions (Sheet 2 of 2)

Base+0x8

Interrupt Identification Register

UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

FIFO

E

S

1

FIFO

E

S

0

re

s

e

rv

e

d

re

s

e

rv

e

d

IID

3

IID

2

IID

1

IP

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

Bits

Name

Description