10 spi interface, 1 boot flash, 2 boot flash selection – Artesyn ATCA-9405 Installation and Use (May 2014) User Manual

Page 83: 1 boot flash 4.10.2 boot flash selection, Table 4-9, P2020 spi chip select assignment, Service processor

Service Processor

ATCA-9405 Installation and Use (6806800M71G)

83

4.10 SPI Interface

The P2020 includes a full duplex four-wire SPI interface. The SPI interface can support up to four

separate SPI devices. The P2020 SPI interface connects to the SPI Boot Flashes, to the Telecom

DPLL and to the Terminal Server. The following table shows the P2020 chip select assignments

for the SPI interface.

4.10.1 Boot Flash

Two SPI Flash devices are provided as P2020 boot devices.

Hardware write protection signal WP# of SPI Flash is pulled down permanently to enable the

hardware protection built in the SPI Flash. Individual Boot Flash sector write protection must be

implemented via software mechanism according to SPI Flash specification.

4.10.2 Boot Flash Selection

For crisis recovery, Boot Flash 1 (default) and Boot Flash 2 (recovery) can be exchanged under

IPMC software control through logic implemented in the FPGA.

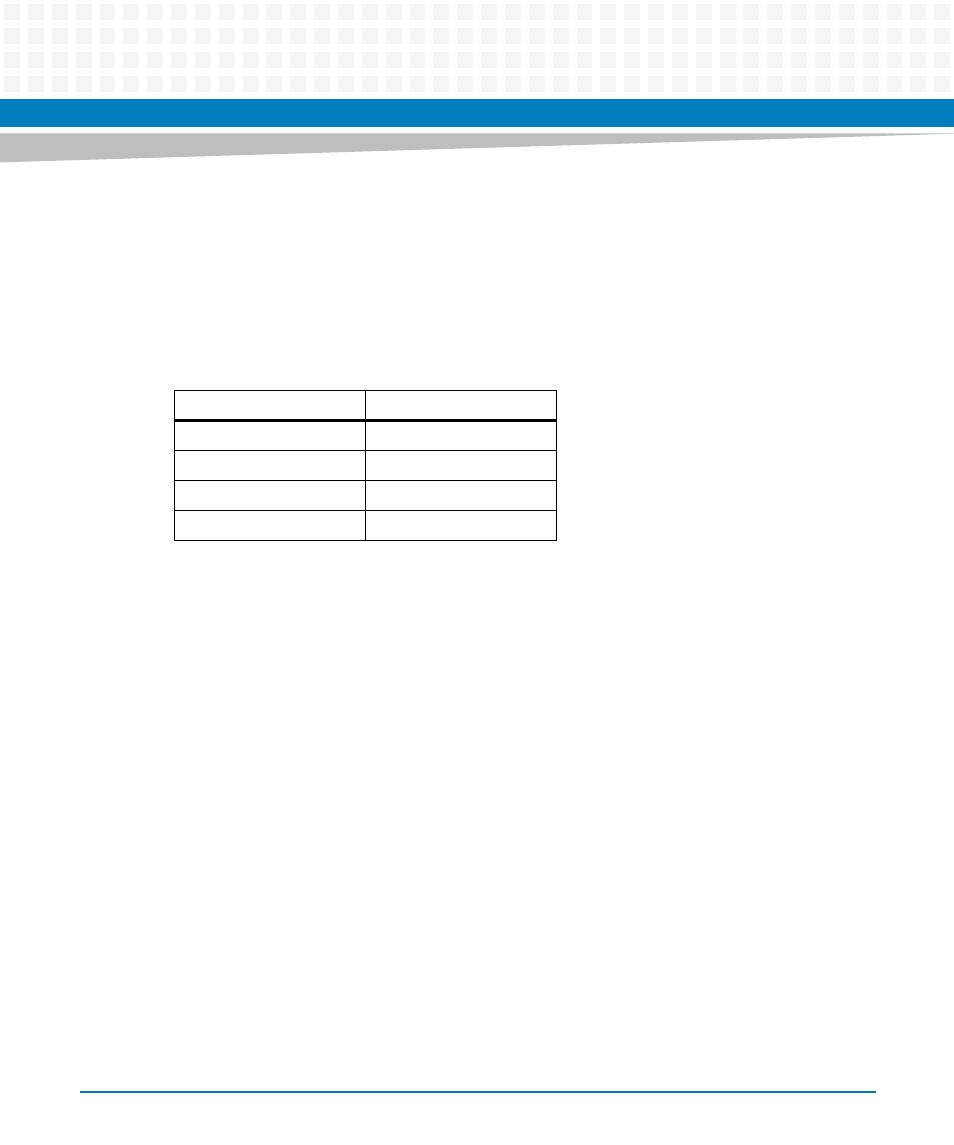

Table 4-9 P2020 SPI Chip Select Assignment

SPI Chip Select

Value

CS0#

SPI Boot Flash 1 (default)

CS1#

SPI Boot Flash 2 (backup)

CS2#

Telecom DPLL

CS3#

Terminal Server