Table 2-4, Switch settings, Hardware preparation and installation – Artesyn ATCA-7365-CE Installation and Use (May 2014) User Manual

Page 54

Hardware Preparation and Installation

ATCA-7365-CE Installation and Use (6806800L73J)

54

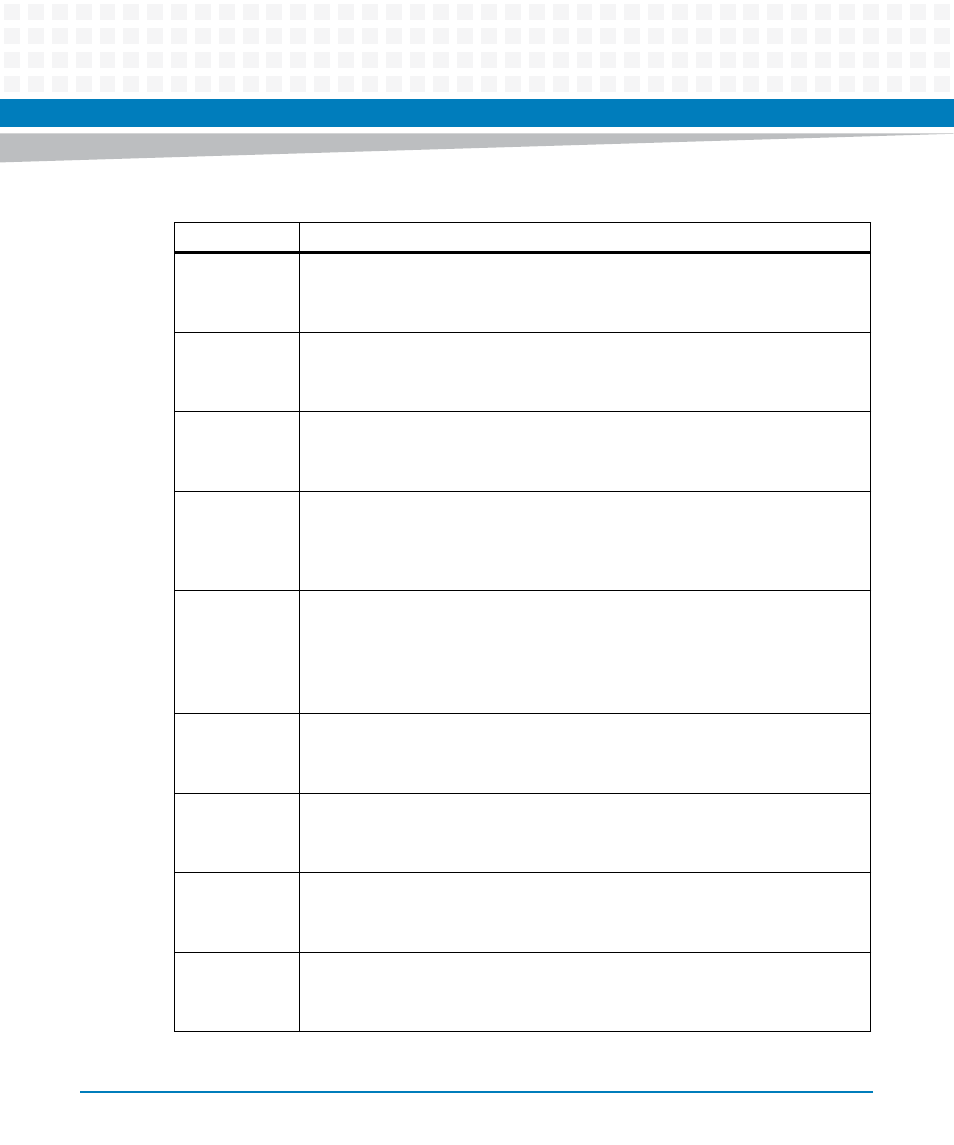

Table 2-4 Switch Settings

Switch

Description

SW1-1

Default Boot-Flash (BIOS) write protection

OFF: Write-enabled (default)

ON: Write-protected

SW1-2

Recovery Boot-Flash (BIOS) write protection

OFF: Write-enabled (default)

ON: Write-protected

SW1-3

TSOP or debug-socket SPI boot select

OFF: Boot from TSOP SPI flash (either Default/Recovery) (default)

ON: Boot from debug socket SPI flash

SW1-4

ICH10 GPIO33-Pinstrap: SPI Flash Descriptor Security Override Strap and ME

disable if sampled LOW

OFF: No SPI Flash Descriptor security override and ME working in S0/S1 (default)

ON: Flash security descriptor and ME disabled (for debugging only)

SW2-1

Serial Line #1 and #2 Routing

OFF: FPGA-COM#1 to face plate, FPGA-COM#2 to RTM (default)

ON: FPGA-COM#1 to RTM, FPGA-COM#2 to face plate

NOTE: IPMC COM1/2 routing selection has precedence. For details, see

.

SW2-2

IPMC Debug Console Routing

OFF: IPMC debug console at 3-pin header (default)

ON: IPMC debug console at face plate instead of FPGA COM

SW2-3

FPGA-Bitstream PROM selection

OFF: FPGA loads from default Bitstream PROM

ON: FPGA loads from Recovery Bitstream PROM

SW2-4

PECI Master selection

OFF: IPMC is PECI master

ON: ICH10 is PECI master

SW3-1

Enable manual “Default SPI Boot Flash” / “Recovery SPI Boot Flash” selection

OFF: IPMI selects boot flash (default)

ON: SW3-2 selects Boot Flash