13 flash status and protection registers, Table 6-64, Flash status register – Artesyn ATCA-7365-CE Installation and Use (May 2014) User Manual

Page 205: Maps and registers

Maps and Registers

ATCA-7365-CE Installation and Use (6806800L73J)

205

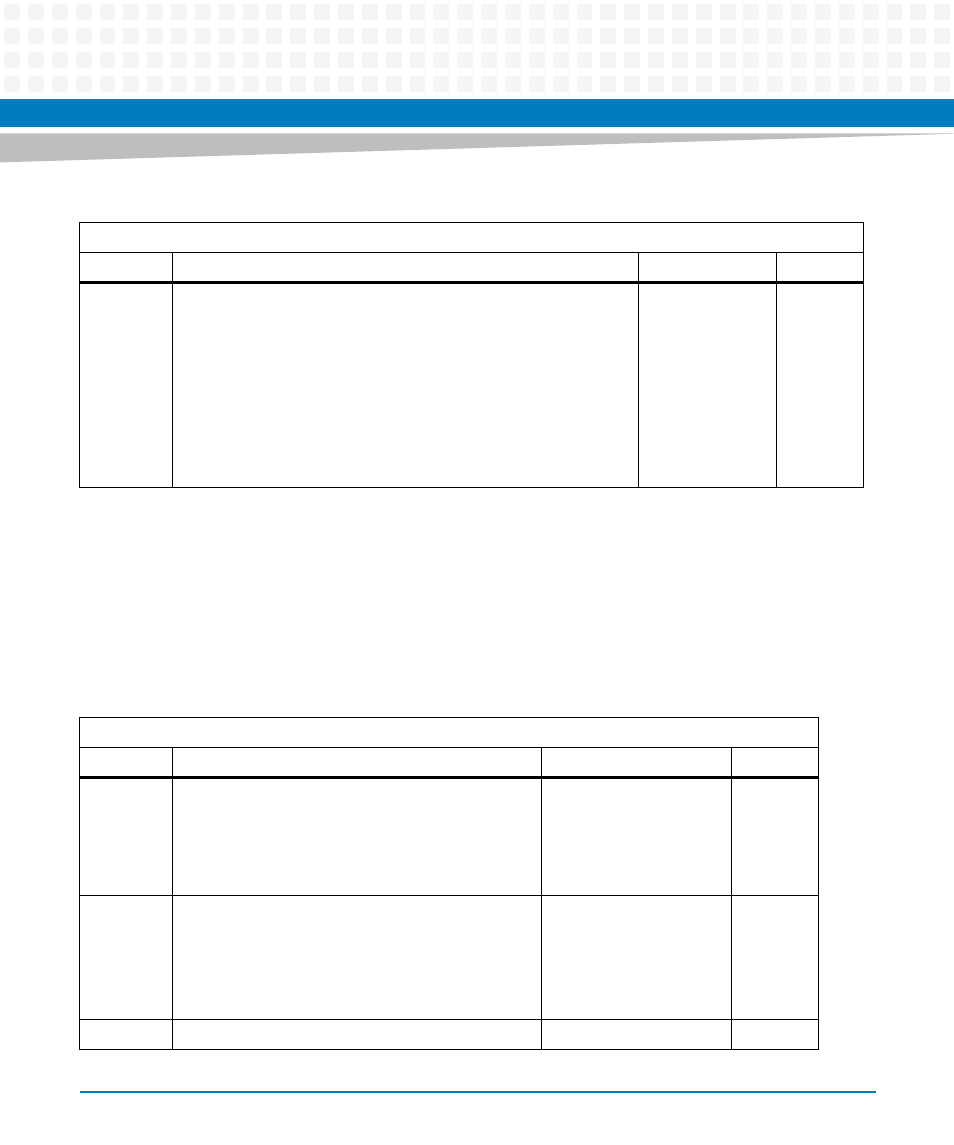

6.4.13 Flash Status and Protection Registers

The flash status register indicates the actual status of the mechanical switches SW1.1 (Signal

BOOT_DEF_WP_), SW1.2 (Signal BOOT_REC_WP_), SW1.3 (Signal BOOT_TSOP), SW3.1

(Signal BOOT_SEL_EN_) and SW3.2 (Signal BOOT_DEFAULT) and the status of IPMC signal

BOOT_SELECT.

7:5

An external Interrupt Signal CPU_IRQ_X_ is used.

Only used when IRQ Frame Number is 0x00:

0x0: Interrupt is masked (disabled).

0x1: Map Interrupt to CPU_IRQ_A_

0x2: Map Interrupt to CPU_IRQ_B_

0x3: Map Interrupt to CPU_IRQ_C_

0x4: Map Interrupt to CPU_IRQ_D_

0x5: Map Interrupt to CPU_IRQ_F_

0x6: Map Interrupt to CPU_IRQ_G_

0x7: Map Interrupt to CPU_IRQ_H_

0

LPC:r/ w

Table 6-63 Interrupt Mask and Map Registers (continued)

Address Offset: 0x23 – 0x2D

Bit

Description

Default

Access

Table 6-64 Flash Status Register

Address Offset: 0x040

Bit

Description

Default

Access

0

Default Boot SPI Flash Write protection Status. See

Default Boot SPI Flash Write Enable register, how to

disable write protection.

0: Default Boot SPI Flash is unprotected

1: Default Boot SPI Flash is protected

Ext. BOOT_DEF_WP_

1

0: SW1.1 OFF

1: SW1.1 ON

LPC: r

1

Recovery Boot SPI Flash Write protection Status. See

Recovery Boot SPI Flash Write Enable register, how to

disable write protection

0: Recovery Boot SPI Flash is unprotected

1: Recovery Boot SPI Flash is protected

Ext. BOOT_REC_WP_

2

0: SW1.2 OFF

1: SW1.2 ON

LPC: r

3:2

Reserved

0

LPC: r