Altera Stratix V Avalon-ST User Manual

Page 41

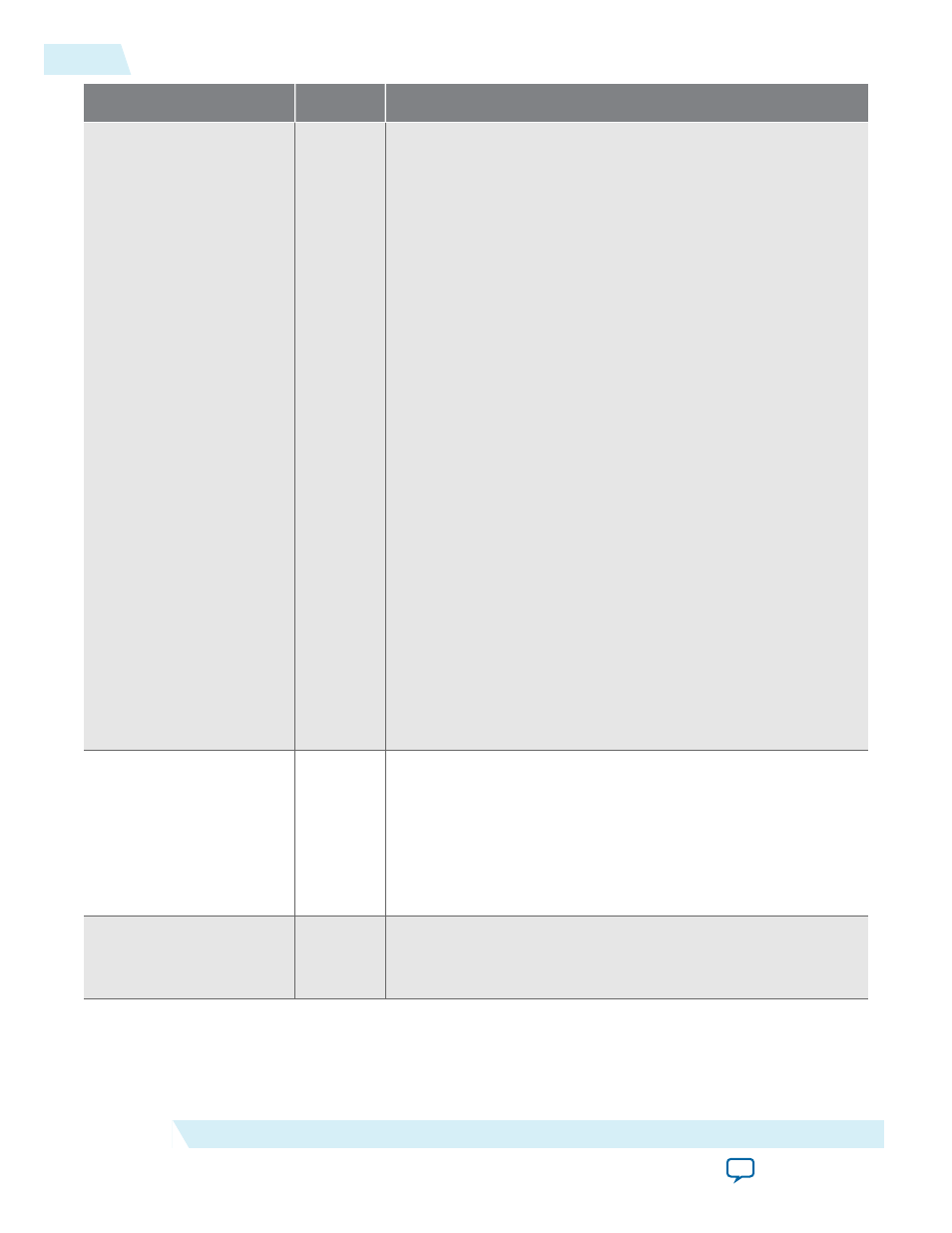

Signal

Direction

Description

qwords contain data, resulting in the following encodings for the

128-and 256-bit interfaces:

• 128-Bit interface:

•

rx_st_empty

= 0,

rx_st_data[127:0]

contains valid data

•

rx_st_empty = 1

,

rx_st_data[63:0]

contains valid data

• 256-bit interface: single packet per cycle mode

•

rx_st_empt

y

= 0,

rx_st_data[255:0]

contains valid

data

•

rx_st_empty

= 1,

rx_st_data[191:0]

contains valid data

•

rx_st_empty

= 2,

rx_st_data[127:0]

contains valid

data

•

rx_st_empty

= 3,

rx_st_data[63:0]

contains valid data

• When the TLP ends in the lower 128 bits, the following

equations apply:

•

rx_st_eop[0]=1 & rx_st_empty[0]=0

,

rx_st_

data[127:0]

contains valid data

•

rx_st_eop[0]=1 & rx_st_empty[0]=1

,

rx_st_

data[63:0]

contains valid data,

rx_st_data[127:64]

is

empty

• When TLP ends in the upper 128bits, the following equations

apply:

•

rx_st_

eop[1]=1 & rx_st_empty[1]=0

,

rx_st_

data[255:128]

contains valid data

•

rx_st_eop[1]=1 & rx_st_empty[1]=1

,

rx_st_

data[191:128]

contains valid data,

rx_st_

data[255:192]

is empty

rx_st_ready

Input

Indicates that the Application Layer is ready to accept data. The

Application Layer deasserts this signal to throttle the data stream.

If

rx_st_ready

is asserted by the Application Layer on cycle

readyLatency

is a ready cycle, during which

the Transaction Layer may assert

valid

and transfer data.

The RX interface supports a

readyLatency

of 2 cycles.

rx_st_valid

Output

Clocks

rx_st_data

into the Application Layer. Deasserts within

2 clocks of

rx_st_ready

deassertion and reasserts within 2 clocks

of

rx_st_ready

assertion if more data is available to send.

4-6

Avalon‑ST RX Interface

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions