Recommended speed grades, Steps in creating a design for pci express – Altera Stratix V Avalon-ST User Manual

Page 10

Related Information

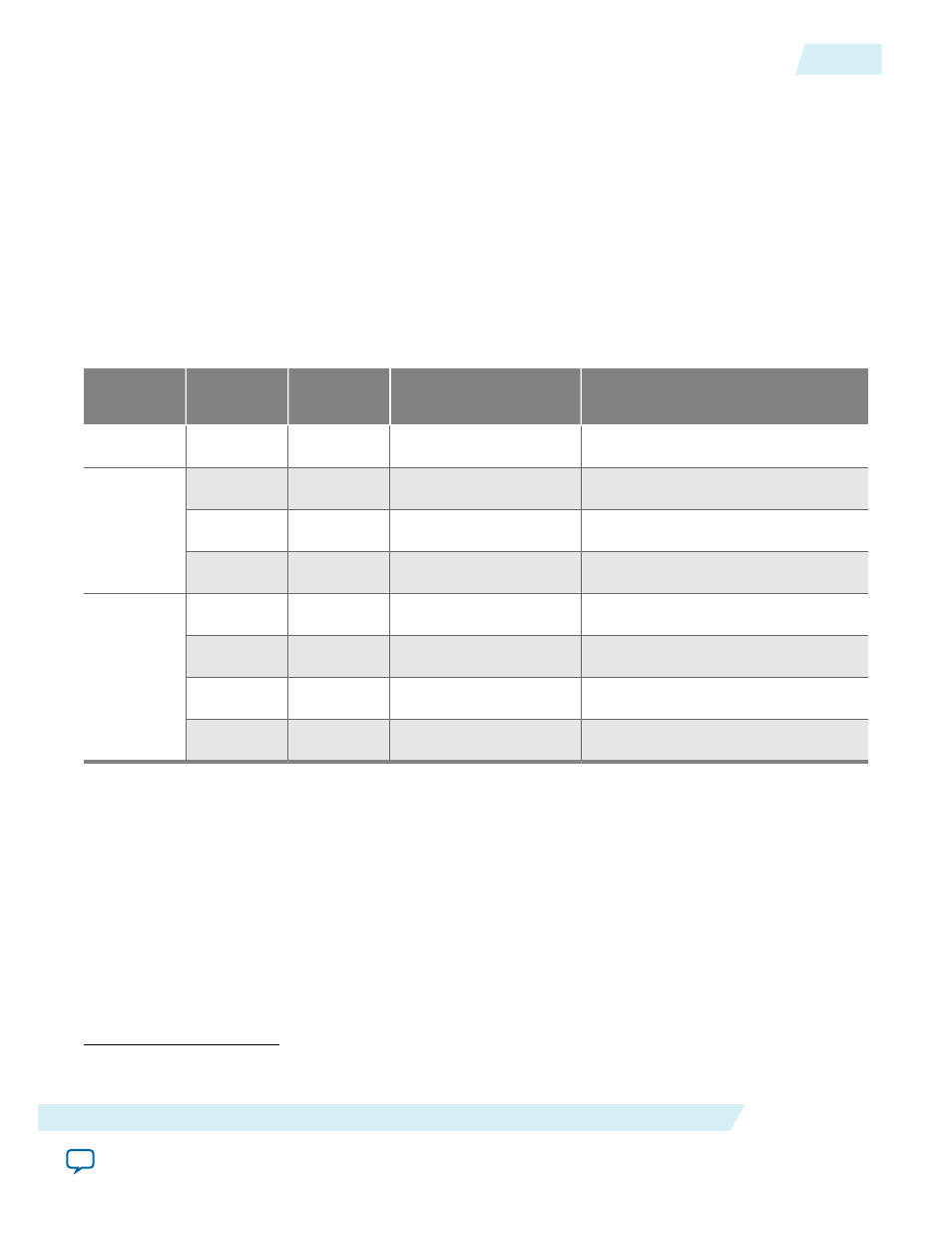

Recommended Speed Grades

Table 1-6: Stratix V Recommended Speed Grades for All SR-IOV Configurations

Altera recommends setting the Quartus II Analysis & Synthesis Settings Optimization Technique to Speed when

the Application Layer clock frequency is 250 MHz. For information about optimizing synthesis, refer to “Setting

Up and Running Analysis and Synthesis in Quartus II Help. For more information about how to effect the

Optimization Technique settings, refer to Area and Timing Optimization in volume 2 of the Quartus II

Handbook. Refer to the Related Links below.

Link Rate

Link Width

Interface

Width

Application Clock

Frequency (MHz)

Recommended Speed Grades

Gen1

×8

128 Bits

125

–1, –2, –3, –4

Gen2

×4

128 bits

125

–1, –2, –3, –4

×8

128 bits

250

–1, –2, –3

(2)

×8

256 bits

125

–1, –2, –3, –4

Gen3

×2

128 bits

125

–1, –2, –3, –4

×4

128 bits

250

–1, –2, –3

(2)

×4

256 bits

125

–1, –2, –3,–4

×8

256 bits

250

–1, –2, –3

(2)

Related Information

•

•

•

Steps in Creating a Design for PCI Express

Before you begin

Select the PCIe variant that best meets your design requirements.

(2)

The -4 speed grade is also possible for this configuration; however, it requires significant effort by the end

user to close timing.

UG-01097_sriov

2014.12.15

Recommended Speed Grades

1-9

Datasheet

Altera Corporation