Base address register (bar) settings – Altera Stratix V Avalon-ST User Manual

Page 25

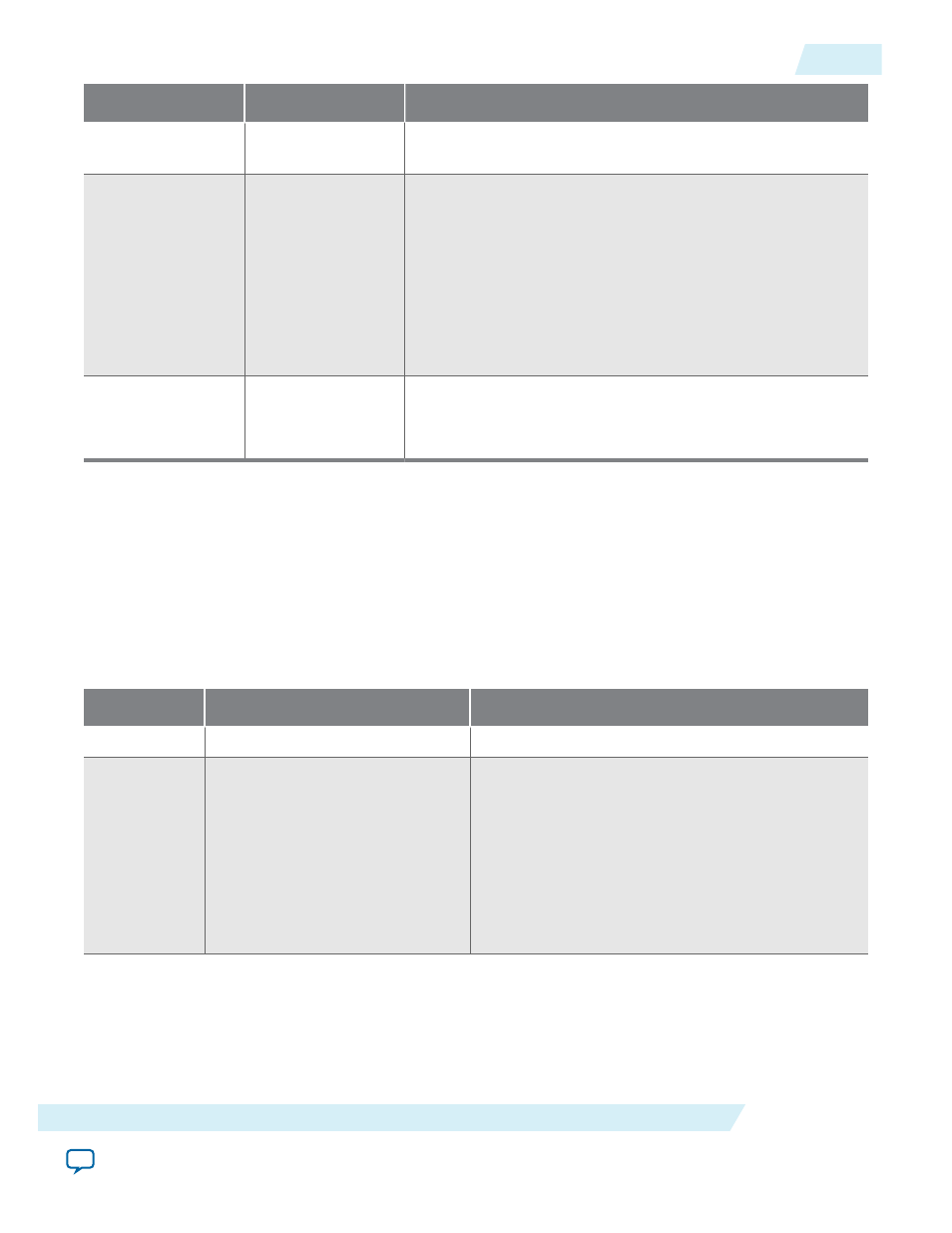

Parameter

Value

Description

Enable SR-IOV

Support

On/Off

Turn this option on to include the SR-IOV functionality.

Enable Alterna‐

tive Routing-ID

(ARI) support

On/Off

This core supports the following configurations:

• 1 PF and 4-7 VFs with no ARI

• 1 PF and 4-128 VFs in multiples of 4 with ARI

• 2 PFs with 4-6 VFs and no ARI

• 2 PFs with 4-128 VFs in multiples of 4 with ARI

Refer to Section 6.1.3 Alternative Routing-ID Interpretation

(ARI) of the PCI Express Base Specification more information

about ARI.

Enable

Functional Level

Reset (FLR)

On/Off

When you turn this option on, each function can be individu‐

ally reset.

Related Information

Base Address Register (BAR) Settings

Each function can implement up to six BARs. You can configure up to six 32-bit BARs or three 64-bit

BARs for both PFs and VFs. The BAR settings are the same for all VFs associated with a PF.

Table 3-2: BAR Registers

Parameter

Value

Description

Present

Enabled/Disabled

Indicates whether or not this BAR is instantiated.

Type

32-bit address

64-bit address

If you select 64-bit address, 2 contiguous BARs are

combined to form a 64-bit BAR. you must set the

higher numbered BAR to Disabled.

If the BAR TYPE of any even BAR is set to 64-bit

memory, the next higher BAR supplies the upper

address bits. The supported combinations for 64-bit

BARs are {BAR1, BAR0}, {BAR3, BAR2}, {BAR4,

BAR5}.

UG-01097_sriov

2014.12.15

Base Address Register (BAR) Settings

3-5

Parameter Settings

Altera Corporation