Altera 100G Interlaken MegaCore Function User Manual

Page 88

This section describes the register values you must program. For instructions to program the registers that

activate the PRBS test feature in your Arria V or Stratix V 100G Interlaken IP core, refer to the hard PCS

register programming instructions in the Native PHY IP Core chapter for your target device family and in

the Transceiver Reconfiguration Controller chapter of the Altera Transceiver PHY IP Core User Guide.

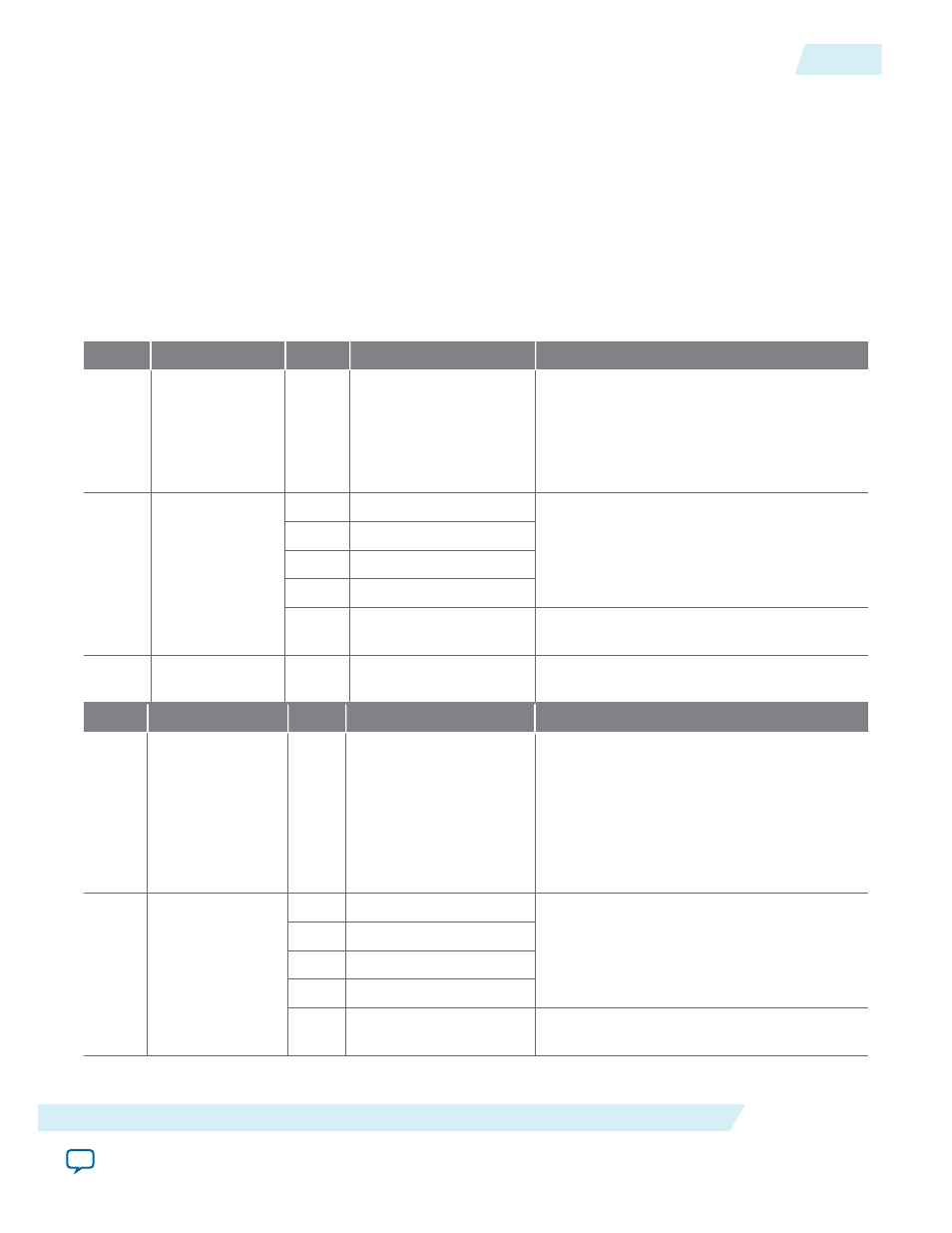

Table 8-2: Programming the Hard PCS Registers in Arria V and Stratix V Devices

To turn on the PRBS feature in the hard PCS, you must program the following hard PCS registers in the order

shown, for each of the TX and RX sides. These registers are not accessible using the 100G Interlaken IP core

Management interface. You must access these registers through the Transceiver Reconfiguration Controller that

connects to the IP core.

Ensure you set these register bits using a read-modify-write register access sequence (per register), to avoid

modifying the other register fields.

TX

Register Offset

Bits

Meaning

Action

1

0x141

[0]

Invert TX channels

Set this bit to the value of 0 to specify that

the outgoing PRBS be inverted, or set this

bit to the value of 1 to specify that the

outgoing PRBS not be inverted. The default

value of this register bit is 0. By default, the

outgoing PRBS is inverted.

2

0x135

[10]

Enable PRBS7

Set one of these bits to the value of 1, and

the others to the value of 0, to select the TX

polynomial.

[8]

Enable PRBS23

[6]

Enable PRBS9

[4]

Enable PRBS31

[3]

TX test enable

Set this bit to the value of 1 to enable the

PRBS pattern generator in the transmitter.

3

0x137

[2]

Enable TX PRBS clock

Set this bit to the value of 1 to enable the

TX PRBS clock.

RX

Register Offset

Bits

Meaning

Action

1

0x16D

[2]

Invert RX channels

Set this bit to the value of 0 to specify that

the PCS should expect the incoming PRBS

to be inverted, or set this bit to the value of

1 to specify that the PCS should not expect

the incoming PRBS to be inverted. The

default value of this bit is 0. In loopback

mode, you should set this bit to match the

setting in the PRBS transmitter.

2

0x15E

[14]

Enable PRBS7

Set one of these bits to the value of 1, and

the others to the value of 0, to select the

expected polynomial.

[13]

Enable PRBS23

[12]

Enable PRBS9

[11]

Enable PRBS31

[10]

RX test enable

Set this bit to the value of 1 to enable the

PRBS pattern verifier in the receiver.

UG-01128

2015.05.04

Setting up PRBS Mode in Arria V and Stratix V Devices

8-3

100G Interlaken IP Core Test Features

Altera Corporation