Altera 100G Interlaken MegaCore Function User Manual

Page 60

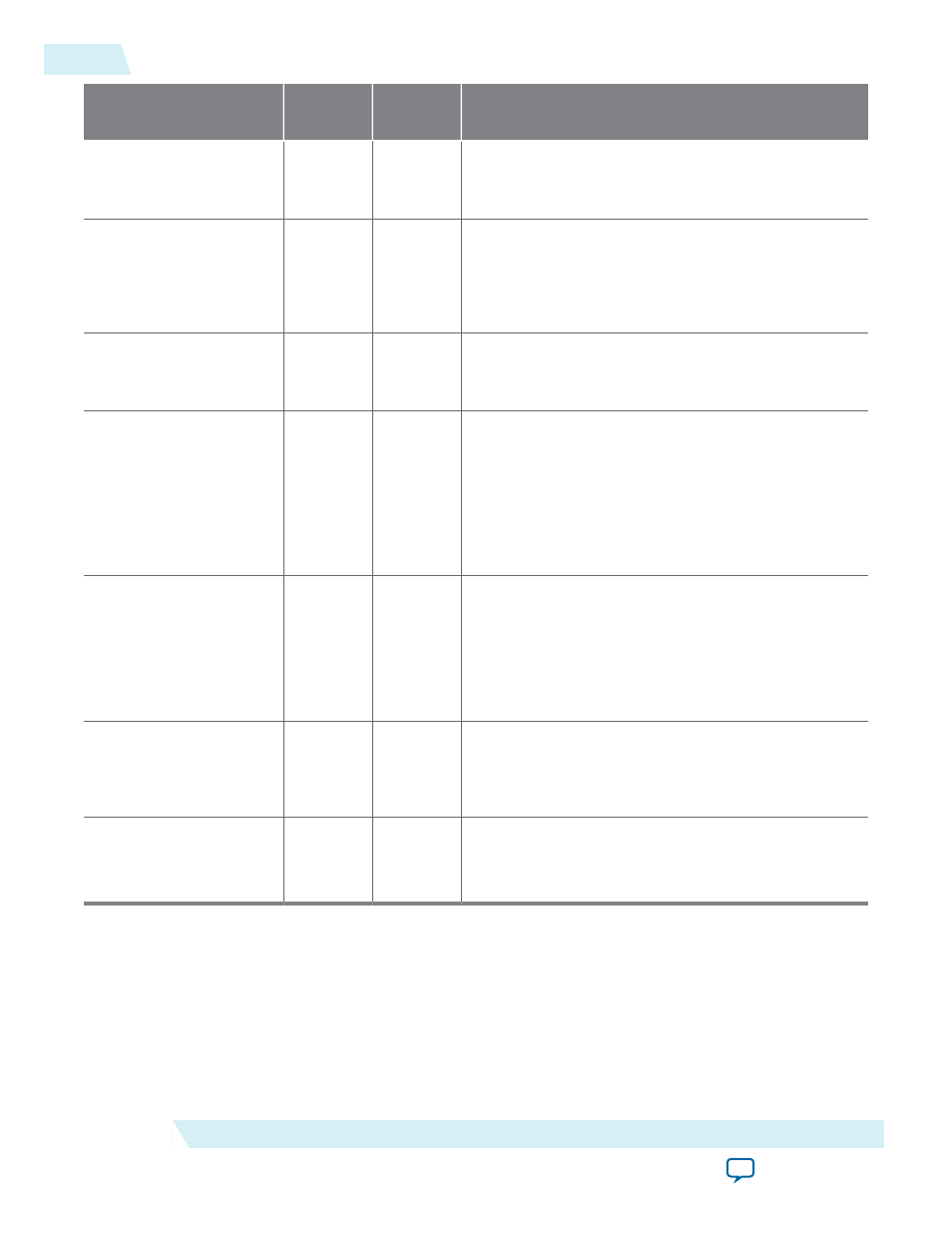

Signal Name

Direction

Width

(Bits)

Description

tx_serial_clk

Input

NUM_

LANES–

Clocks for the individual transceiver channels in

100G Interlaken IP core variations that target an Arria

10 device.

clk_tx_common

Output

1

PCS common lane clock driven by the SERDES

transmit PLL. The clock rate is the lane rate divided

by 40 bits. The

clk_tx_common

frequency is

156.25 MHz for 6.25 Gbps, 257.8 MHz for

10.3125 Gbps, and 312.5 MHz for 12.5 Gbps per lane.

clk_rx_common

Output

1

Master recovered lane clock. The Interlaken specifica‐

tion requires all incoming lanes to run at the same

frequency.

tx_usr_clk

Input

1

Transmit side user data interface clock. To achieve

100 Gbps Ethernet traffic throughput, you must run

this clock at one of the following minimum frequen‐

cies:

• 225 MHz in dual segment mode, 12-lane variations

• 300 MHz in single segment mode and in 24-lane

variations

rx_usr_clk

Input

1

Receive side user data interface clock. To achieve 100

Gbps Ethernet traffic throughput, you must run this

clock at one of the following minimum frequencies:

• 225 MHz in dual segment mode, 12-lane variations

• 300 MHz in single segment mode and in 24-lane

variations

mm_clk

Input

1

Management clock. Clocks the register accesses. It is

also used for clock rate monitoring and some analog

calibration procedures. You must run this clock at a

frequency in the range of 100 MHz–125 MHz.

reconfig_clk

Input

1

Clocks the Arria 10 transceiver reconfiguration

interface. This clock is available only in IP core

variations that target an Arria 10 device. You should

run this clock at a frequency of 100 MHz.

Related Information

Performance and Fmax Requirements for 100G Ethernet Traffic

Explains the

tx_usr_clk

and

rx_usr_clk

frequency requirements.

5-2

100G Interlaken IP Core Clock Interface Signals

UG-01128

2015.05.04

Altera Corporation

100G Interlaken MegaCore Function Signals