100g interlaken ip core reset interface signals, 100g interlaken ip core reset interface signals -3 – Altera 100G Interlaken MegaCore Function User Manual

Page 61

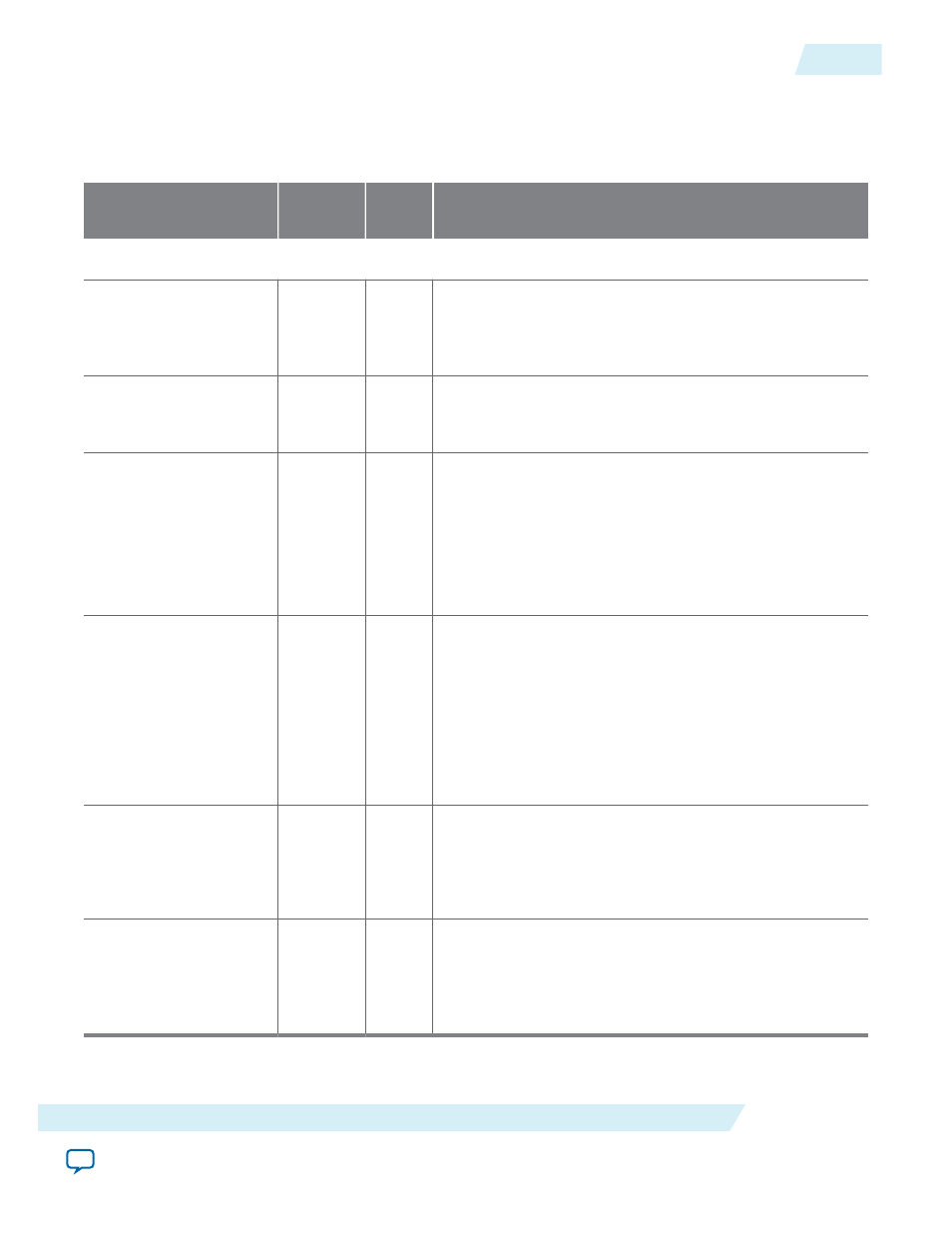

100G Interlaken IP Core Reset Interface Signals

Table 5-3: 100G Interlaken IP Core Reset Interface

Signal Name

Direction

Width

(Bits)

Description

100G Interlaken IP Core Reset Signals

reset_n

Input

1

Active-low reset signal for the 100G Interlaken IP core.

Altera recommends that you hold this signal low for at

least the duration of two

mm_clk

cycles, to ensure the reset

sequence proceeds correctly.

reconfig_reset

Input

1

Reset signal for the Arria 10 transceiver reconfiguration

interface. This signal is available only in IP core variations

that target an Arria 10 device.

srst_tx_common

Output

1

Synchronous reset signal that the IP core asserts high

while the transmitter is initializing. This signal is synchro‐

nous with

clk_tx_common

.

This signal goes low to indicate that the transceiver PLL

has locked to the reference clock. The TX PCS and the TX

MAC are held in reset while the

srst_tx_common

clock is

asserted. You can use this signal for diagnostic purposes.

srst_rx_common

Output

1

Synchronous reset that is active at startup. This signal is

synchronous with

clk_rx_common

. This signal goes low to

indicate that the transceiver PLL has achieved lock and the

recovered clock has locked to data in normal operation,

this signal is deasserted after the transceiver completes its

reset sequence. The RX PCS and the RX MAC are held in

reset while the

srst_rx_common

clock is asserted. This

signal is also active in the event of a serious clock data

recovery failure on any of the RX lanes.

tx_usr_srst

Output

1

Transmit side reset output signal. Indicates the transmit

side user data interface is resetting. This signal is synchro‐

nous with

tx_usr_clk.

Your application can use this

signal to reset any status counters you may maintain in the

tx_usr_clk

domain.

rx_usr_srst

Output

1

Receive side reset output signal. Indicates the receive side

user data interface is resetting. This signal is synchronous

with

rx_usr_clk.

Your application can use this signal to

reset any status counters you may maintain in the

rx_

usr_clk

domain.

UG-01128

2015.05.04

100G Interlaken IP Core Reset Interface Signals

5-3

100G Interlaken MegaCore Function Signals

Altera Corporation