Altera 100G Interlaken MegaCore Function User Manual

Page 67

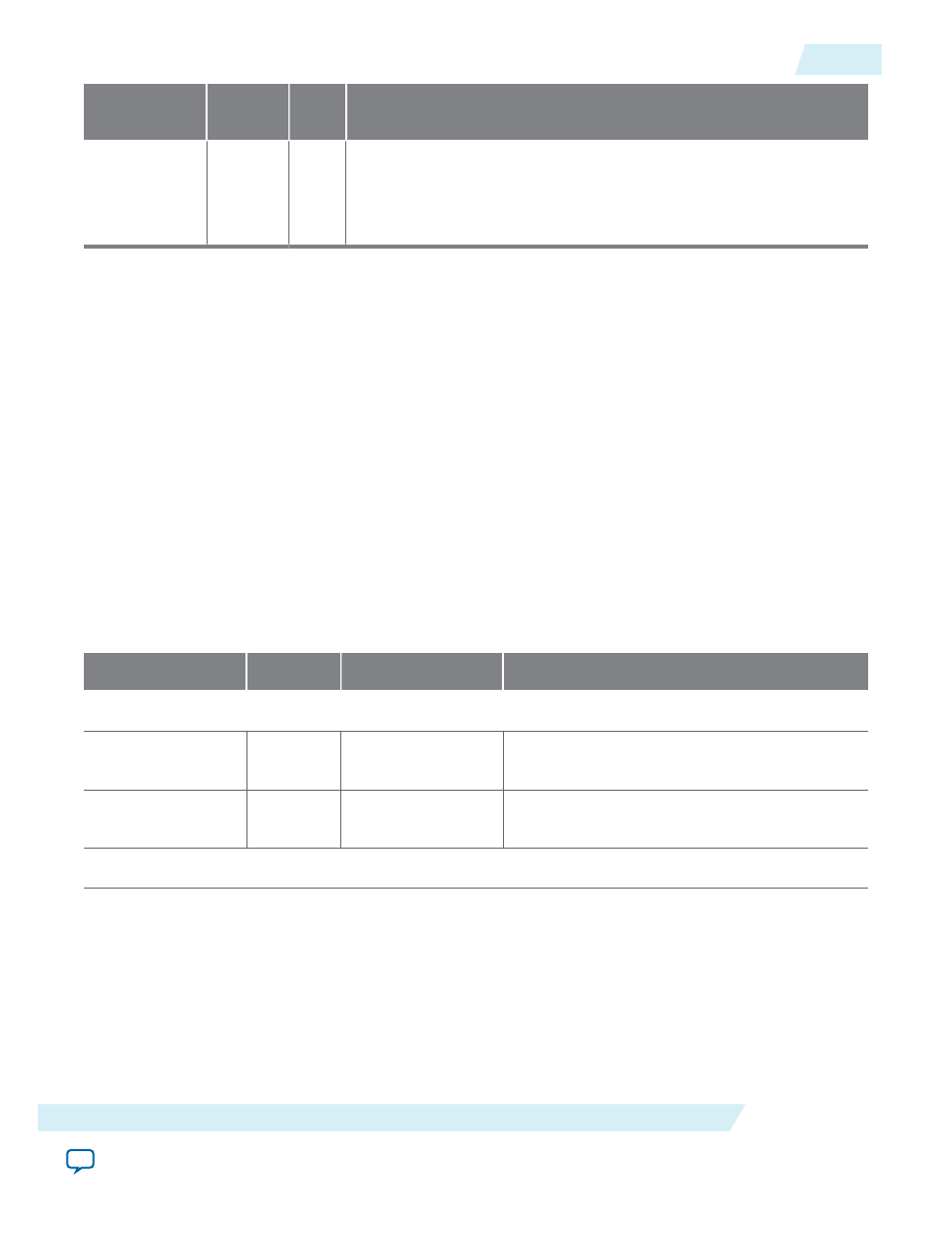

Signal Name

Direction Width

(Bits)

Description

irx_err

Output

1

Indicates an errored packet. This signal is valid only when both

irx_num_valid[7:4]

and

irx_eopbits[3:0]

are non-zero. When a

CRC24 or other error occurs, the 100G Interlaken IP core asserts this

signal for all open channel packets to label them all as errored packets,

because the IP core cannot assign the error to a specific channel.

Related Information

•

Describes the parameter to select single segment or dual segment mode.

•

on page 4-8

Describes the dual segment mode.

•

100G Interlaken IP Core RX Errored Packet Handling

on page 4-24

Describes the behavior of the

irx_err

signal.

•

on page 3-6

Describes the parameter to select Packet or Interleaved mode.

•

on page 4-7

Describes the Packet and Interleaved modes.

100G Interlaken IP Core Interlaken Link and Miscellaneous Interface

Signals

Table 5-5: 100G Interlaken IP Core SERDES Signals, Burst Parameter Signals, and Real Time Status Signals

Signal Name

Direction

Width (Bits)

Description

SERDES Pins

rx_pin

Input

Number of lanes

Receiver SERDES data pin on the RX Interlaken

link.

tx_pin

Output

Number of lanes

Transmit SERDES data pin on the TX

Interlaken link.

TX Burst Control Settings

UG-01128

2015.05.04

100G Interlaken IP Core Interlaken Link and Miscellaneous Interface Signals

5-9

100G Interlaken MegaCore Function Signals

Altera Corporation