100g interlaken ip core receiver side example – Altera 100G Interlaken MegaCore Function User Manual

Page 50

100G Interlaken IP Core Receive User Data Interface Examples

The following examples illustrate how to use the Altera 100G Interlaken IP core RX user data interface:

100G Interlaken IP Core Receiver Side Example

100G Interlaken IP Core Dual Segment Interleaved Data Transfer Receive Example

100G Interlaken IP Core Receiver Side Example

The 100G Interlaken IP Core can generate interleaved data transfers on the RX user data transfer

interface. The IP core always toggles the

irx_sob

and

irx_eob

signals to indicate the beginning of the

burst and end of the burst. In single segment mode, only

irx_sob[1]

toggles. In dual segment mode,

irx_sob[0]

toggles if the current burst starts at word 4 of the data symbol.

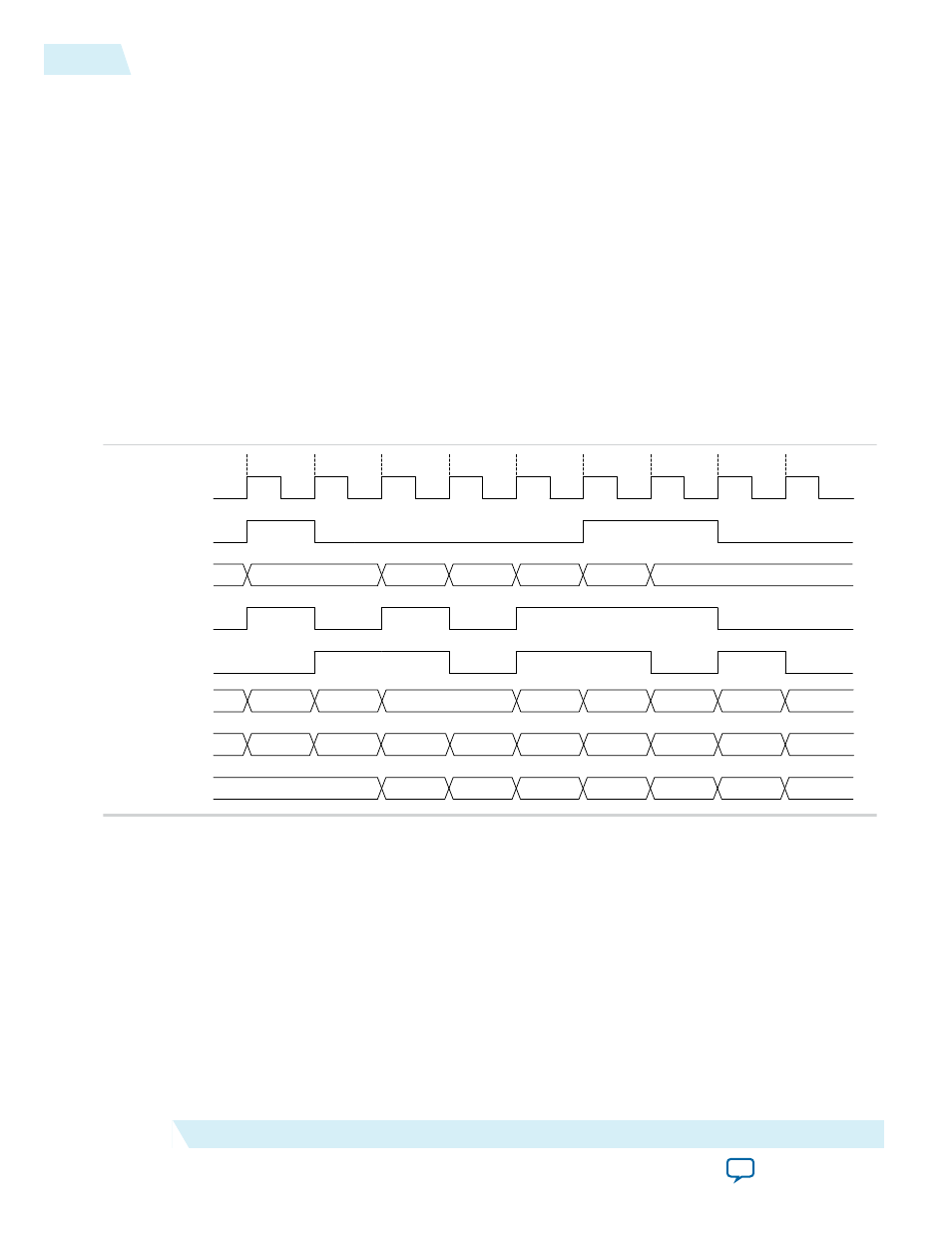

Figure 4-10: 100G Interlaken IP Core Receiver Side Single Segment Example

This example illustrates the expected behavior of the 100G Interlaken IP core application interface receive

signals during data transfers from the IP core to the application on the RX user data transfer interface in

interleaved, single segment mode.

Cycle 1

Cycle 2

Cycle 3

Cycle 4

Cycle 5

Cycle 6

Cycle 7

Cycle 8

Cycle 9

rx_usr_clk

irx_sop[1]

irx_sob[1]

irx_eob

irx_dout_words

d1

4’b1000

4’b1000

4’b0011

4’b0010

4’b1000

4’b0000

4’b0000

4’b0000

4’b0000

4’b0000

4’b1011

4’b1011

4’b0000

4’b1000

4’b1000

d2

d3

d4

d5

d6

d7

irx_num_valid[7:4]

irx_eopbits

irx_chan

8’h2

8’h4

8’h4

8’h3

8’h2

The figure shows the timing diagram for an interleaved data transfer in Interleaved mode. In cycle 1, the

IP core asserts

irx_sop[1]

and

irx_sob[1]

, indicating that this cycle is both the start of the burst and the

start of the packet. The first word is MSB aligned at the top. The value the IP core drives on

irx_chan

indicates the data targets channel 2. You must sample

irx_chan

during cycles in which

irx_sob[1]

is

asserted. The

irx_chan

output signal is not guaranteed to remain valid for the duration of the burst.

In cycle 2, the IP core asserts

irx_eob

, indicating the data the IP core transfers to the application in this

clock cycle is the end of the burst.

irx_num_valid[7:4]

indicates all eight words are valid. However, the

data in this cycle is not end of packet data. The IP core will transfer at least one additional data burst in

this packet, possibly interleaved with one or more bursts in packets that target different data channels.

Cycle 3 is a short burst with both

irx_sob[1]

and

irx_eob

asserted. The IP core drives the value of three

on

irx_num_valid[7:4]

to indicate that three words of the eight-word

irx_dout_words

data bus are

valid. The data is packed in the most significant words of

irx_dout_words

.The IP core drives the value of

4-20

100G Interlaken IP Core Receive User Data Interface Examples

UG-01128

2015.05.04

Altera Corporation

Functional Description