Altera 100G Interlaken MegaCore Function User Manual

Page 109

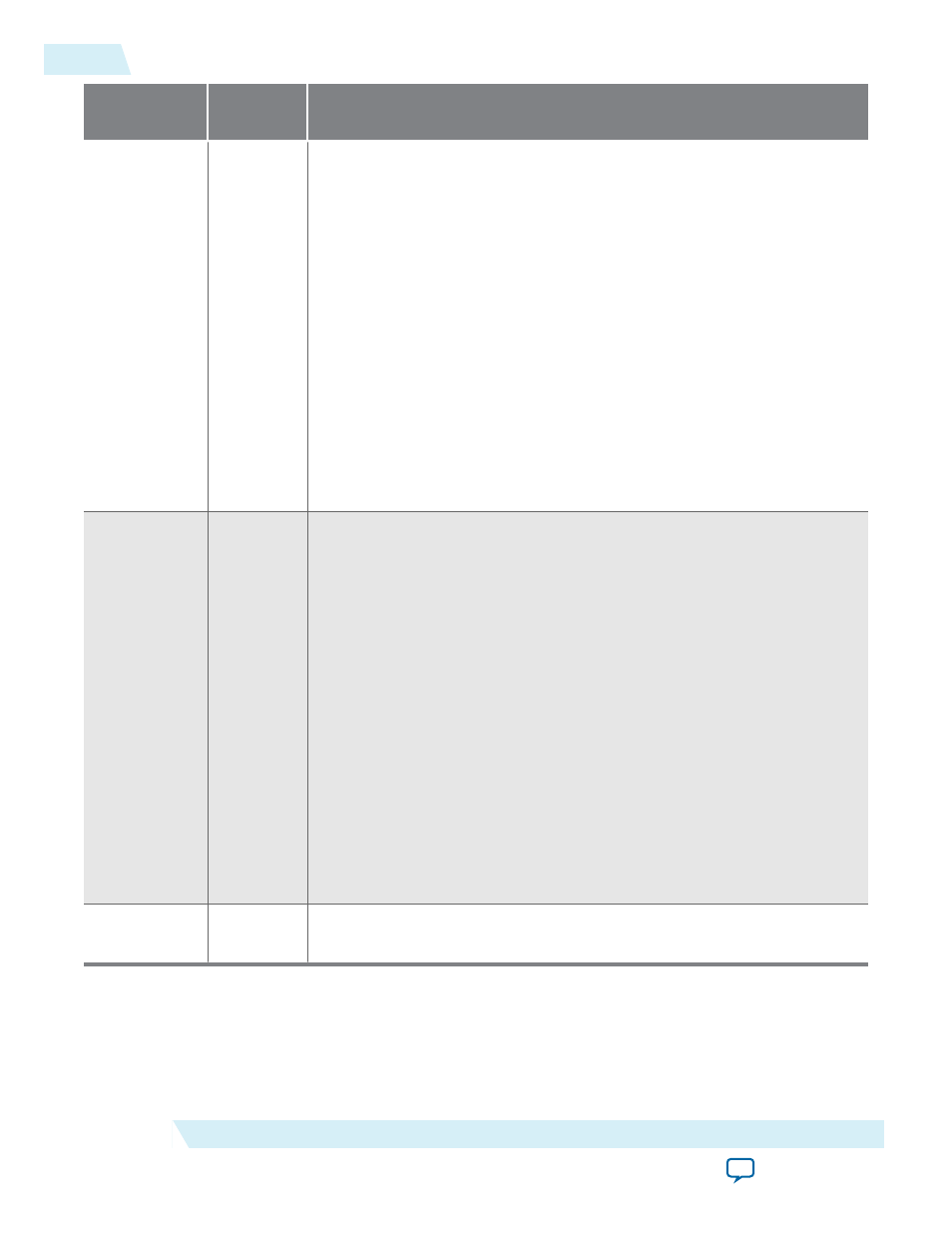

Date

ACDS

Version

Changes Made

May 2013

13.0

(2013.05.06)

• Documented the new dual segment mode, including:

• New Received data format parameter in the 100G Interlaken

parameter editor.

• Changed user data transfer signal widths.

• Added new

itx_ifc_err

signal.

• Expanded Fmax requirements discussion to include the dual segment

mode case.

• Documented the new Transfer mode selection parameter in the 100G

Interlaken parameter editor. Previously this parameter was hidden (TX_

PKTMOD_ONLY).

• Documented new error handling features, including changes to and

renaming of

irx_crc_24_err

signal to

irx_err

.

• Added PRBS support. Changes include addition of new hard PCS

registers.

• Added support for CRC-32 error injection.

• Updated device speed grade information.

• Modified document format.

February

2013

12.1 SP1

• Reformatted figures.

• Modified Figure 4–1 on page 4–2, Figure 4–2 on page 4–4, Figure 5–1 on

page 5–10, and Figure 5–2 on page 5–10 for readability.

• Removed mention of OpenCore evaluation feature from “100G

Interlaken IP Core Evaluation Features” on page 1–5 because the feature

name caused confusion with the OpenCore Plus evaluation feature. The

current and past descriptions of the evaluation features are correct.

• Added default parameter values in Chapter 3, Parameter Settings and in

Chapter 7, Advanced Parameter Settings.

• Renamed Appendix A, Performance and Fmax Requirements for 100G

Ethernet Traffic.

• Consolidated information about 100G Interlaken MegaCore function

license. All variations of this IP core are available if you have a single

Altera license for this IP core.

• Enhanced description of RX and TX data paths in new sections

“Transmit Path Blocks” on page 4–9 and “Receive Path Blocks” on

page 4–13.

• Corrected location of “Receiver Side Timing Diagrams” on page 4–10 to

“Receive Path” on page 4–10.

November

2012

12.1

Initial release.

B-4

Document Revision History

UG-01128

2015.05.04

Altera Corporation

Additional Information