Adding the reconfiguration controller, Adding the reconfiguration controller -10 – Altera 100G Interlaken MegaCore Function User Manual

Page 20

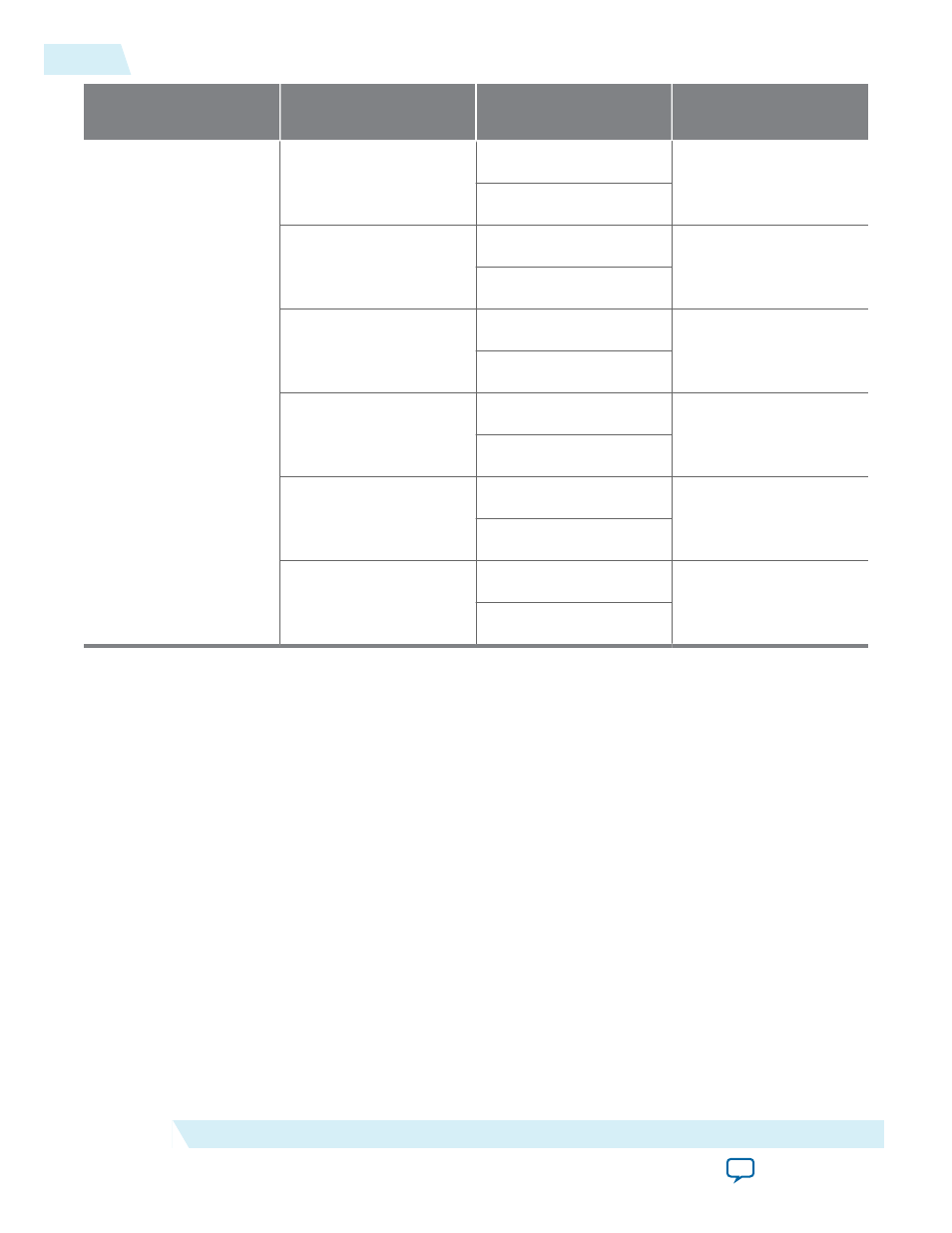

Transceiver Block Number Logical Channel Number in

Device

Direction

Interlaken Lane Number in

IP Core

0

5

TX

5

RX

4

TX

4

RX

3

TX

3

RX

2

TX

2

RX

1

TX

1

RX

0

TX

0

RX

For example, in an Arria V or Stratix V device, to change the VOD setting for lane 9, you write logical

channel 10 to the Reconfiguration Controller.

Related Information

Background information to better understand logical channel numbering.

Adding the Reconfiguration Controller

100G Interlaken IP core variations that target an Arria V or a Stratix V device require an external reconfi‐

guration controller to function correctly in hardware. 100G Interlaken IP core variations that target an

Arria 10 device include a reconfiguration controller block and do not require an external reconfiguration

controller.

Keeping the Reconfiguration Controller external to the IP core in Arria V and Stratix V devices provides

the flexibility to share the Reconfiguration Controller among multiple IP cores and to accommodate

FPGA transceiver layouts based on the usage model of your application. In Arria 10 devices, you can

configure individual transceiver channels flexibly through an Avalon-MM Arria 10 transceiver reconfigu‐

ration interface.

2-10

Adding the Reconfiguration Controller

UG-01128

2015.05.04

Altera Corporation

Getting Started With the 100G Interlaken IP Core