Device dependent signals, Device dependent signals -14 – Altera 100G Interlaken MegaCore Function User Manual

Page 72

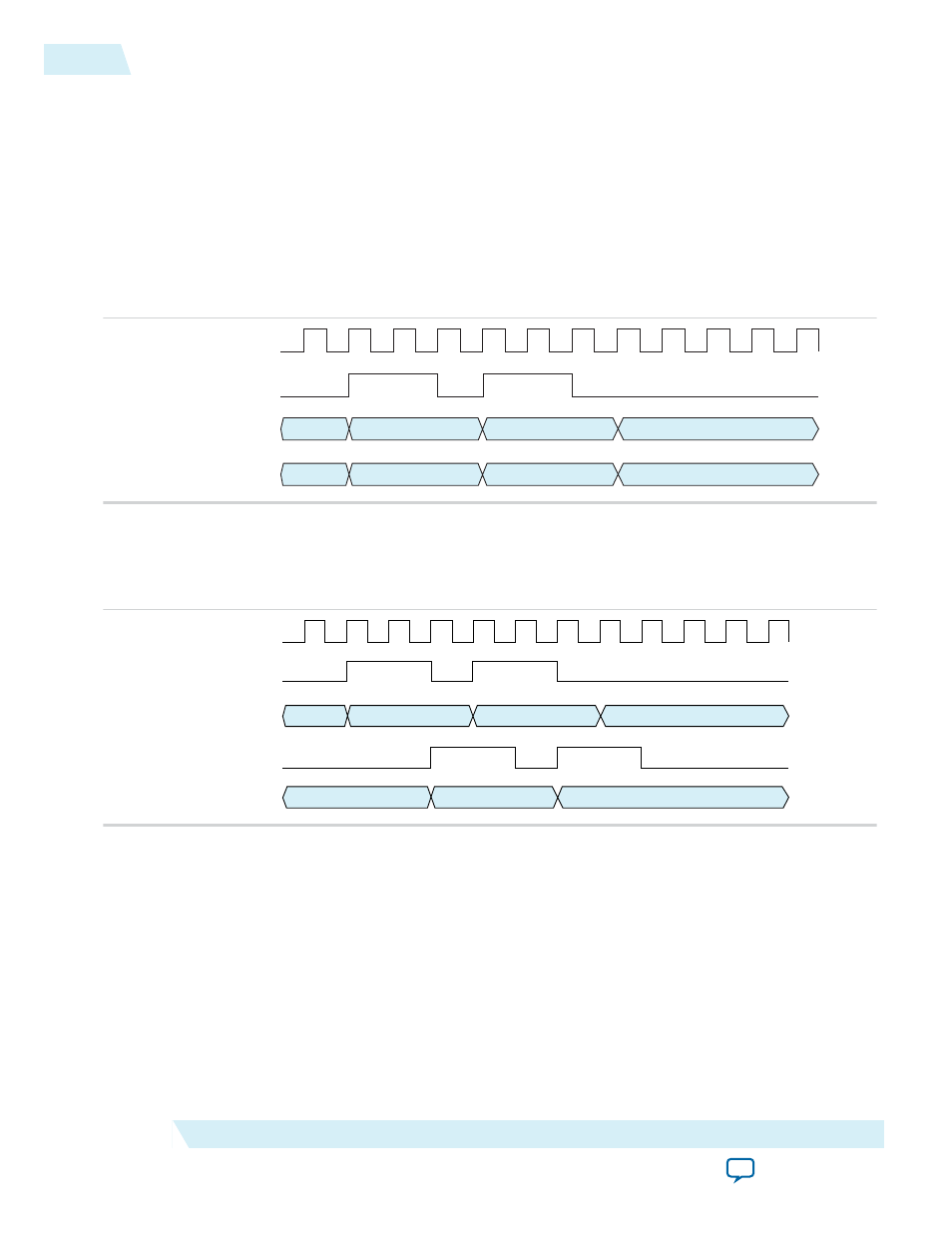

If you use the management interface, drive the control lines as shown in the examples and observing the

following constraints:

• During a write operation, you must maintain the the

mm_write

signal asserted for at least two clock

cycles. Back-to-back writes must be separated by at least one clock cycle.

• During a read operation, you must maintain the

mm_read

signal asserted for at least two clock cycles.

Back-to-back reads must be separated by at least one clock cycle.

Figure 5-1: 100G Interlaken IP Core Management Interface Write Operation

Shows the timing requirements for a write operation on the 100G Interlaken IP core management

interface.

mm_clk

mm_write

mm_addr[15:0]

mm_wdata[31:0]

Don’t Care

0x0012

0x0013

Don’t Care

Don’t Care

wdata0

wdata1

Don’t Care

Figure 5-2: 100G Interlaken IP Core Management Interface Read Operation

Shows the timing requirements for a read operation on the 100G Interlaken IP core management

interface. The IP core asserts the

mm_rdata_valid

signal two cycles after the

mm_read

signal is asserted.

mm_clk

mm_read

mm_addr[15:0]

mm_rdata_valid

mm_rdata[31:0]

Don’t Care

0x0000

0x0001

Don’t Care

Previous Value

rdata0

rdata1

Related Information

Device Dependent Signals

Some of the 100G Interlaken MegaCore function signals depend on the device that your variation targets.

Variations that target an Arria V device or a Stratix V device have an interface to connect to an Altera

Transceiver Reconfiguration Controller that you must instantiate outside the 100G Interlaken IP core for

successful functioning in hardware. Variations that target an Arria 10 device have Arria 10-specific

5-14

Device Dependent Signals

UG-01128

2015.05.04

Altera Corporation

100G Interlaken MegaCore Function Signals