Simulation flow, Simulation flow –5 – Altera SerialLite II IP Core User Manual

Page 91

Chapter 5: Testbench

5–5

Simulation Flow

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

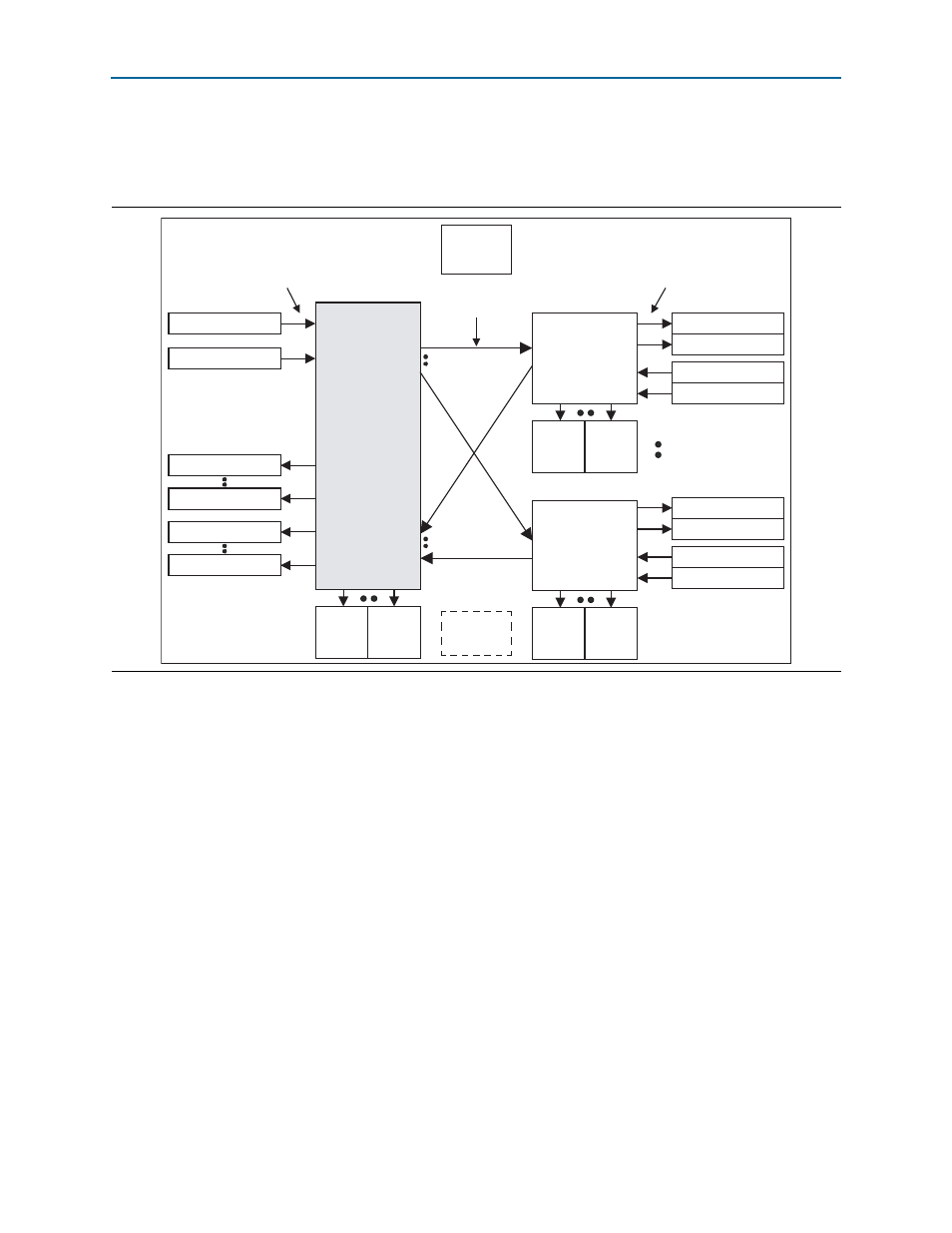

shows the testbench environment for a SerialLite II standard

broadcast mode MegaCore function with multiple SISTER instances that have one

receive and transmit port.

Simulation Flow

This section describes the basic steps to use the SerialLite II testbench. The SerialLite II

testbench performs the following tests, if applicable:

■

The testbench waits for the main reset sequence to end.

■

The testbench waits for both SerialLite II links to come up (DUT and SISTER).

■

If the regular data port is enabled, the testbench begins to send data from the data

port Atlantic generators (DUT and SISTER side). The data Atlantic monitors check

that the first data matches the first data sent from the generators and so on, until

all the data is sent.

■

In Verilog HDL only, if the priority data port is enabled, the testbench begins to

send data from the priority port Atlantic generators. The priority Atlantic

monitors checks that the first priority data matches the first priority data sent from

the generator and so on, until all the data is sent.

Once all monitors receive the last packet, the testbench finishes.

You can use the SerialLite II testbench as a template for creating your own testbench

or modify it to increase the testing coverage.

Figure 5–4. SerialLite II Testbench Environment, Verilog HDL Only (Standard Broadcast Mode)

sl2_top

(IP Functional

Simulation Model)

DUT

sl2_top_sister

(IP Functional

Simulation Model)

SISTER0

Atlantic

Interface

Atlantic

Interface

SerialLite II

High-Speed

Interface

SerialLite II Testbench

AGEN_DAT_DUT

AGEN_PRI_DUT

AMON_DAT_DUT0

AMON_DAT_DUTN-1

AMON_PRI_DUTN-1

AMON_PRI_DUT0

AMON_DAT_SIS0

AMON_PRI_SIS0

AGEN_DAT_SIS0

AGEN_PRI_SIS0

sl2_top_sister

(IP Functional

Simulation Model)

SISTERN-1

AMON_DAT_SISN-1

AMON_PRI_SISN-1

AGEN_DAT_SISN-1

AGEN_PRI_SISN-1

Clock and

Reset

Generator

Status

Monitor 1

(SISTER

N-1)

Status

Monitor X

(SISTER

N-1)

Status

Monitor 1

(SISTER

0)

Status

Monitor X

(SISTER

0)

Status

Monitor 1

(DUT)

Status

Monitor X

(DUT)

Custom

PHY IP

Core