Altera SerialLite II IP Core User Manual

Page 105

Chapter 5: Testbench

5–19

Example Testbench – Verilog HDL

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

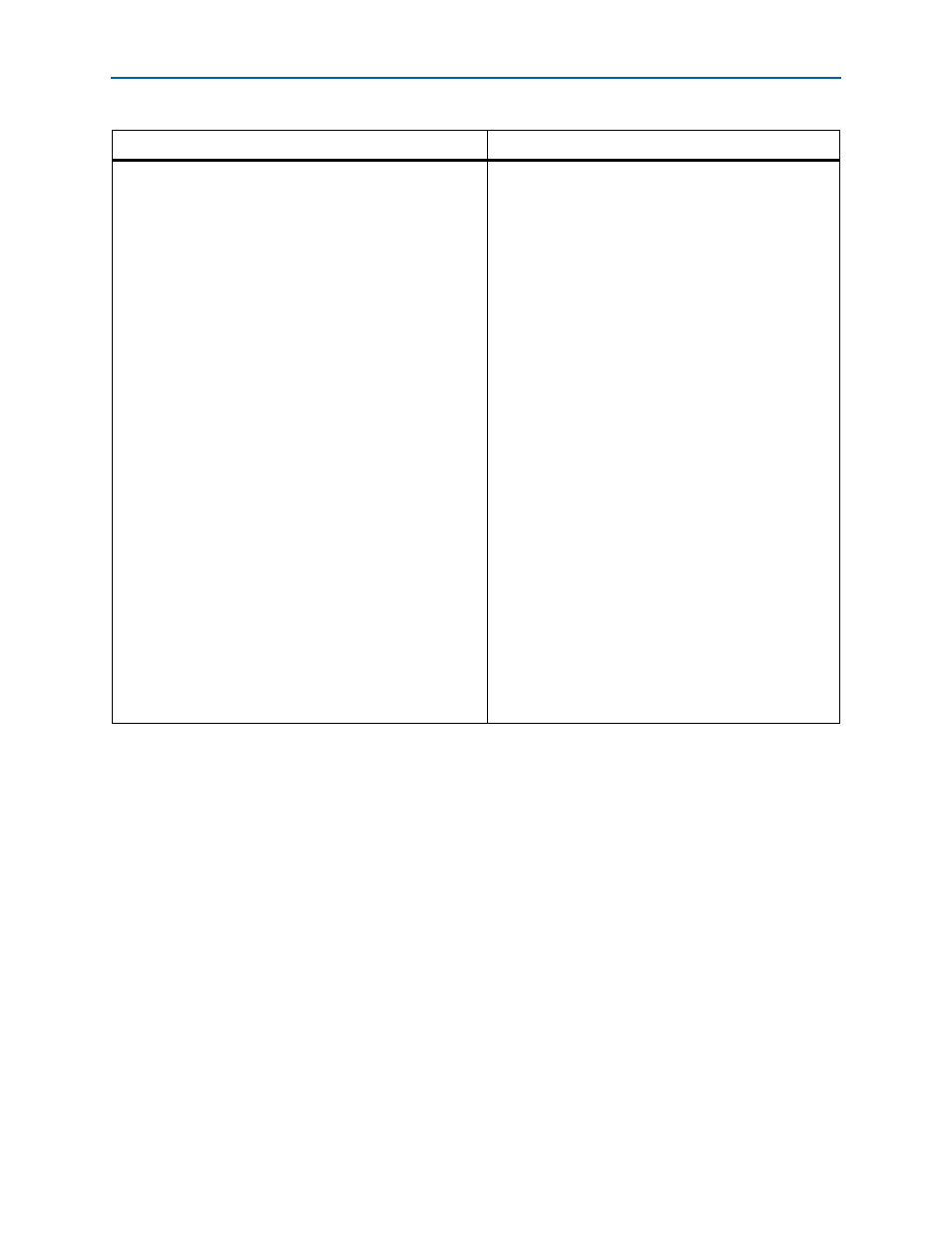

begin

/////////////////////////////////////////////

/

// Generate RDP packets for SISTER

/////////////////////////////////////////////

/

@(posedge trefclk);

agen_dat_sis.verbose(1);

agen_dat_sis.ipg(0,5);

amon_dat_dut.verbose(1);

fork

while ( pkt_cnt_dat_sis > 0 ) begin :

send_loop_dat_sis

integer size;

integer err;

reg [7:0] addr;

addr = $dist_uniform(seed,0,255);

size = $dist_uniform(seed,1,1024);

err = $dist_uniform(seed,0,1);

agen_dat_sis.send_packet(addr,size,err);

reset_watchdog_timer;

pkt_cnt_dat_sis = pkt_cnt_dat_sis - 1;

end

begin

amon_dat_dut.wait_all_packets(packets_to_send

);

end

join

end

Send regular data packets (on Atlantic interface) to the

SISTER MegaCore function.

AGEN and AMON instantiations are set to display verbose

messages.

Set AGEN to insert random inner packet gaps.

Launch two processes in parallel:

- Send regular data packets to the SISTER.

Define packet size, error, address.

Packet address is a random number from 0 to 255.

Packet size is a random number from 1 to 1,024.

Packet err is a random number from 0 to 1.

Call the AGEN send packet task (regular data, SISTER).

Reset watchdog with every packet being sent.

Repeat this loop pkt_cnt_dat_sis times.

- Wait for the other side (Atlantic interface of the DUT) to

receive all these packets.

Table 5–12. Example of a Demonstration Testbench (Part 3 of 5)

Main Section

Comments