Functional description, Interface overview, Chapter 4. functional description – Altera SerialLite II IP Core User Manual

Page 55: Interface overview –1

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

4. Functional Description

The SerialLite II MegaCore function consists of parameterized logic and a

parameterized testbench. The following sections detail the various possible

configurations and things you should consider when deciding how to configure the

link.

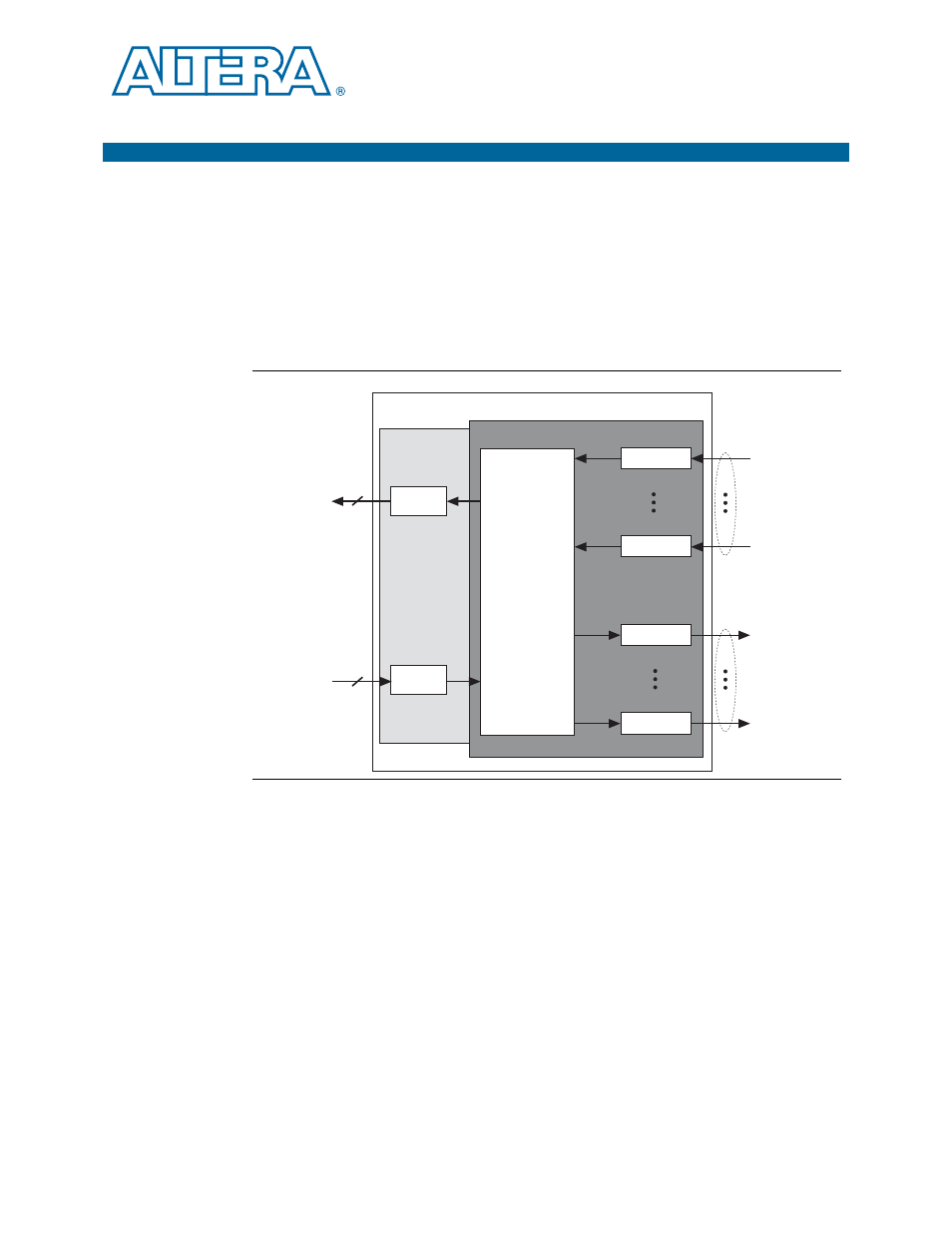

shows a block diagram of the SerialLite II MegaCore function.

f

Refer to

for more information on the test bench.

As shown in

, the SerialLite II MegaCore function is divided into two main

blocks: a protocol processing portion (data link layer) and a high-speed front end

(physical layer). The protocol processing portion features Atlantic FIFO buffers for

data storage or clock domain crossing, as well as data encapsulation and extraction

logic. The high-speed front end contains a link state machine (LSM) and

serializer/deserializer (SERDES) blocks. The SERDES blocks contain optional high-

speed serial clock and data recovery (CDR) logic implemented with high-speed serial

transceivers.

Interface Overview

The SerialLite II MegaCore function has two interfaces, the Atlantic interface and a

high-speed serial interface.

Figure 4–1. SerialLite II MegaCore Function Block Diagram

SerialLite II MegaCore Function

PHY Layer (PCS)

n-bit

Data

Flow

n-bit

n-bit

Receiver

n-bit

Atlantic

Interface

Atlantic

Interface

Data

Flow

SERDES

SERDES

SERDES

SERDES

Word Aligner

Training Detection

Link State Machine

& Generator

Transmitter

SerialLite II

Interface

SerialLite II

Interface

Link Layer