Altera SerialLite II IP Core User Manual

Page 39

3–16

Chapter 3: Parameter Settings

Link Layer Configuration

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

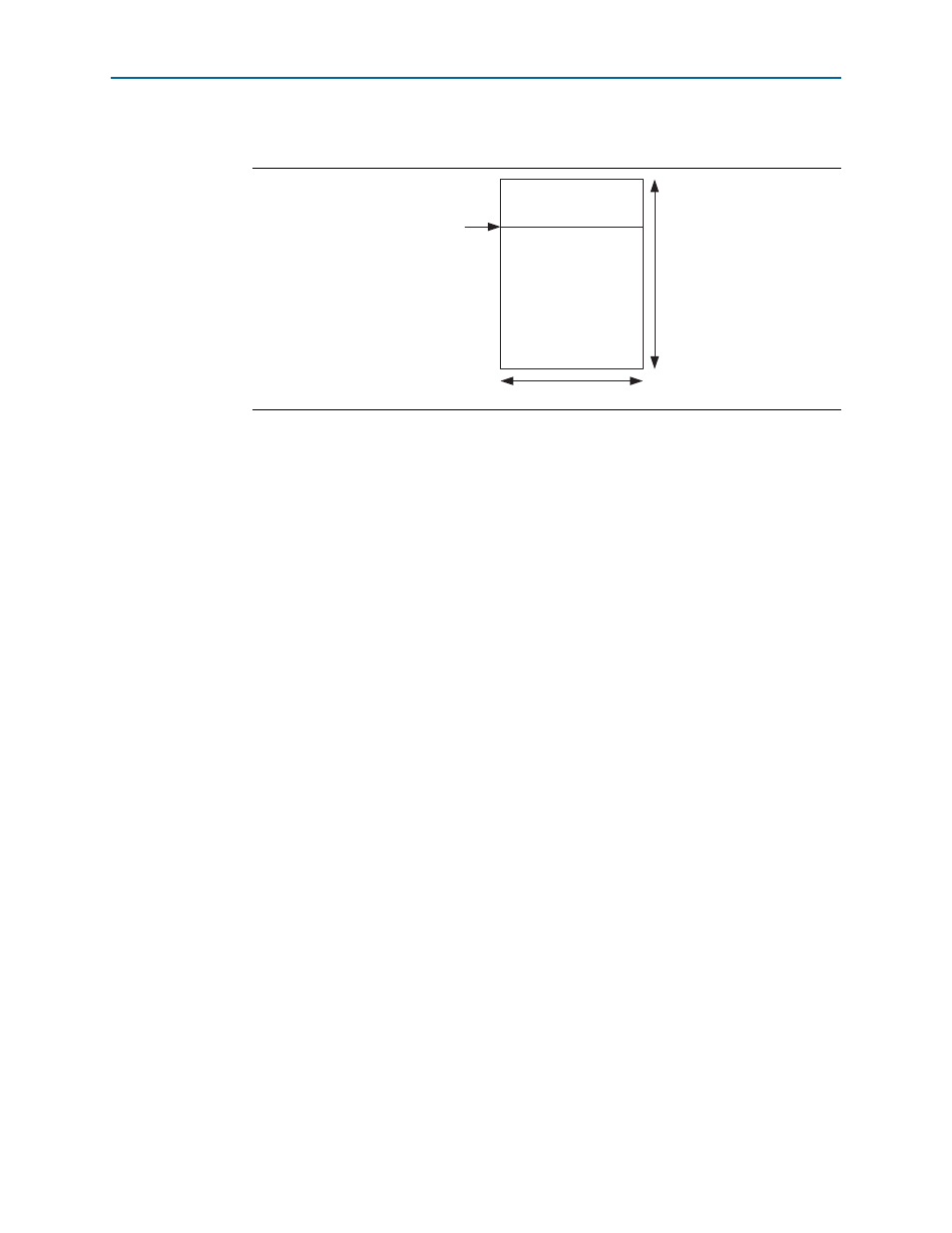

shows the FIFO buffer structure with flow control enabled.

The threshold value determines if a Flow Control PAUSE is requested. You control the

size of this threshold by setting the flow control threshold per port using the

SerialLite II parameter editor to fall within the total depth of the FIFO. The value for

the flow control threshold signals (ctrl_rr_rdp_fcthresh and

ctrl_rr_hpp_fcthresh

) must be within the total FIFO depth. The value must also

ensure required headroom to compensate for the delays for the flow control request to

take effect, and for the remaining data already in the system to be stored in the FIFO.

Refer to section

“Selecting the Proper Threshold Value” on page 3–18

for further

analysis.

The total depth of the FIFO (in bytes) is derived by the SerialLite II parameter editor

using the following formula :

Total Depth = FIFO SIZE /(TSIZE * RX_NUMBER_LANES)

In this example, set the FIFO SIZE on the Parameter Settings tab, Link Layer page by

selecting a value in the Receiver field of the Buffer Size section.

TSIZE

and the RX_NUMBER_LANES are set on the Physical Layer page. Under Data

Settings

, select the TSIZE by selecting a number in the Transfer size option. To set

RX_NUMBER_LANES

, specify a value for the Number of lanes option in the Receiver

Settings

section.

If in this example you select a high-priority FIFO SIZE of 1,024B, and a TSIZE of 2 in a

four-lane SerialLite II configuration, you compute the Total Depth as follows:

Total Depth =1024/2*4 =128

Based on the above result, for this example, you must set the Threshold value in the

SerialLite II parameter editor to be less than 128 elements. Set the Threshold value in

the appropriate packet settings section on the Link Layer page.

Figure 3–11. FIFO Buffer Structure (Flow Control Enabled)

Threshold

Headroom

Primary Flow

Control Threshold

(ctrl_rr_rdp_fcthresh/

ctrl_rr_hpp_fcthresh)

Total depth

of the FIFO

FIFO Width