Link consistency, Physical layer configuration, Data rate – Altera SerialLite II IP Core User Manual

Page 25: Data rate –2

3–2

Chapter 3: Parameter Settings

Link Consistency

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

■

Whether to implement flow control

■

How to size the FIFO buffers

Link Consistency

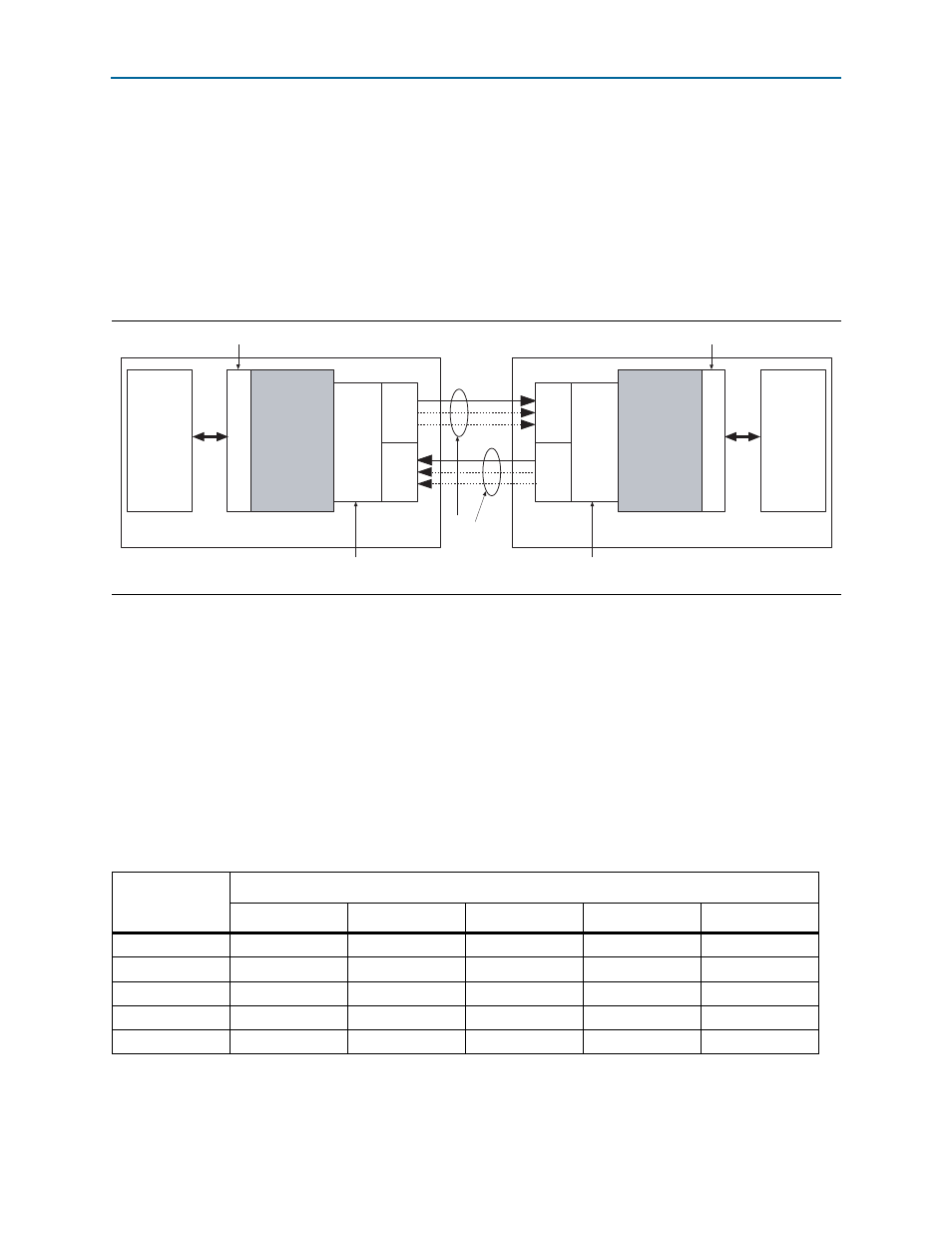

A SerialLite II link consists of two instantiations of logic implementing the

SerialLite II protocol. Each end of the link has a transmitter and a receiver, as shown in

.

Physical Layer Configuration

This section describes the options available to parameterize the physical layer of your

SerialLite II MegaCore function variation.

Data Rate

The SerialLite II MegaCore function supports a data rate range of 622 to 6,375 Mbps

per lane. In Arria II GX devices, the data rate must be less than 3,750 Mbps, and in

Stratix IV devices, less than 6,375 Mbps. The data rate range varies based on the

device and the transfer size (TSIZE) as

illustrates.

Figure 3–1. Complete SerialLite II Link

FPGA 2

SerialLite II

System

FPGA 1

SerialLite II

MegaCore

System

Logic

Logic

One or

more lanes

Tx

Rx

Rx

Tx

Atlantic Interface

Atlantic Interface

High-Speed

Transceivers

High-Speed

Transceivers

Function

Variation

MegaCore

Function

Variation

Table 3–2. Data Rate Dependencies on Transfer Size (Part 1 of 2)

Devices

Data Rate

2.5 Gbps

3.125 Gbps

3.75 Gbps

5 Gbps

6.375 Gbps

Arria II GX

TSIZE= 1, 2

TSIZE= 2

TSIZE= 2

Not Supported

Not Supported

Arria V

TSIZE= 1, 2

TSIZE= 4

TSIZE= 4

Arria V GZ

TSIZE= 1, 2

TSIZE= 4

TSIZE= 4

Cyclone V

TSIZE= 2

TSIZE= 2

TSIZE= 2

TSIZE= 4

Not Supported

Stratix IV

TSIZE= 1, 2

TSIZE= 2

TSIZE= 2

TSIZE= 2

TSIZE= 4