Scramble, De-scramble, Broadcast mode – Altera SerialLite II IP Core User Manual

Page 32: Scramble –9 de-scramble –9 broadcast mode –9

Chapter 3: Parameter Settings

3–9

Physical Layer Configuration

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

Scramble

Scrambling the data eliminates repeating characters, which affect the EMI

substantially at high data rates. A linear feedback shift register (LSFR) is used as a

pseudo-random number generator to scramble the data, using the following

polynomial equation:

G(x) = X

16

+ X

5

+ X

4

+ X

3

+ 1

The transmitted bits are XORed with the output of the LFSR in the data stream. At the

receiver, the data stream is again XORed with an identical scrambler to recover the

original bits. To synchronize the transmitter to the receiver, the COM character

initializes the LFSR with the initial seed of 0×FFFF XORed with the lane number (LN).

Scrambling is recommended for data rates greater than 3,125 Mbps, and is optional

for lower data rates (622 to 3,125 Mbps inclusive). This parameter applies only to the

transmitter, and allows for scrambling (like CRC) to be enabled in one direction only,

as required.

De-Scramble

This parameter applies only to the receiver, and allows for descrambling (like CRC) to

be enabled in one direction only, as required. Descrambling is required if the incoming

data stream is scrambled.

Broadcast Mode

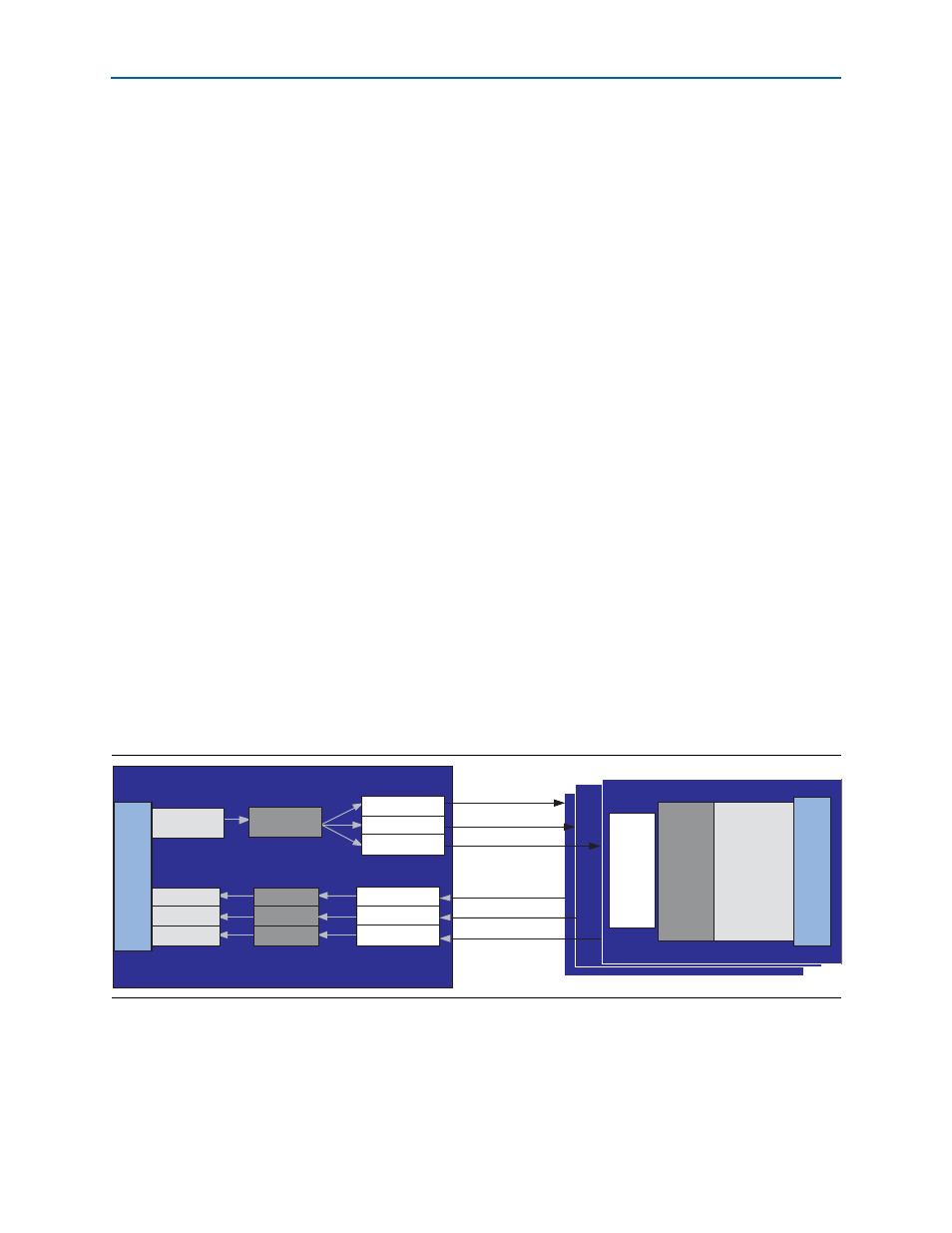

If you enable the broadcast mode parameter for the transmitter, you configure the

MegaCore function to use a single shared transmitter and multiple receivers in the

master device, as shown in

and

. The number of receivers is

determined by the number of lanes chosen for the slave receiver. The master

transmitter uses its output lanes to broadcast identical messages to all slave receivers,

and each slave responds individually by sharing the master's lanes.

Figure 3–8. Broadcast Mode Block Diagram

Master FPGA

Broadcast message

Broadcast message

Broadcast message

N-return

lanes

Shared TX

Link

RX Link 1

RX Link 2

RX Link N

Atlantic

Interface

Shared TX

PHY

RX PHY 1

RX PHY 2

RX PHY N

TX Tsvr 1

TX Tsvr 2

TX Tsvr N

RX Tsvr 1

RX Tsvr 2

RX Tsvr N

Slave FPGA N

Light-weight

Linklayer

PHY

Layer

CDR

SERDES

Atlantic

Interface