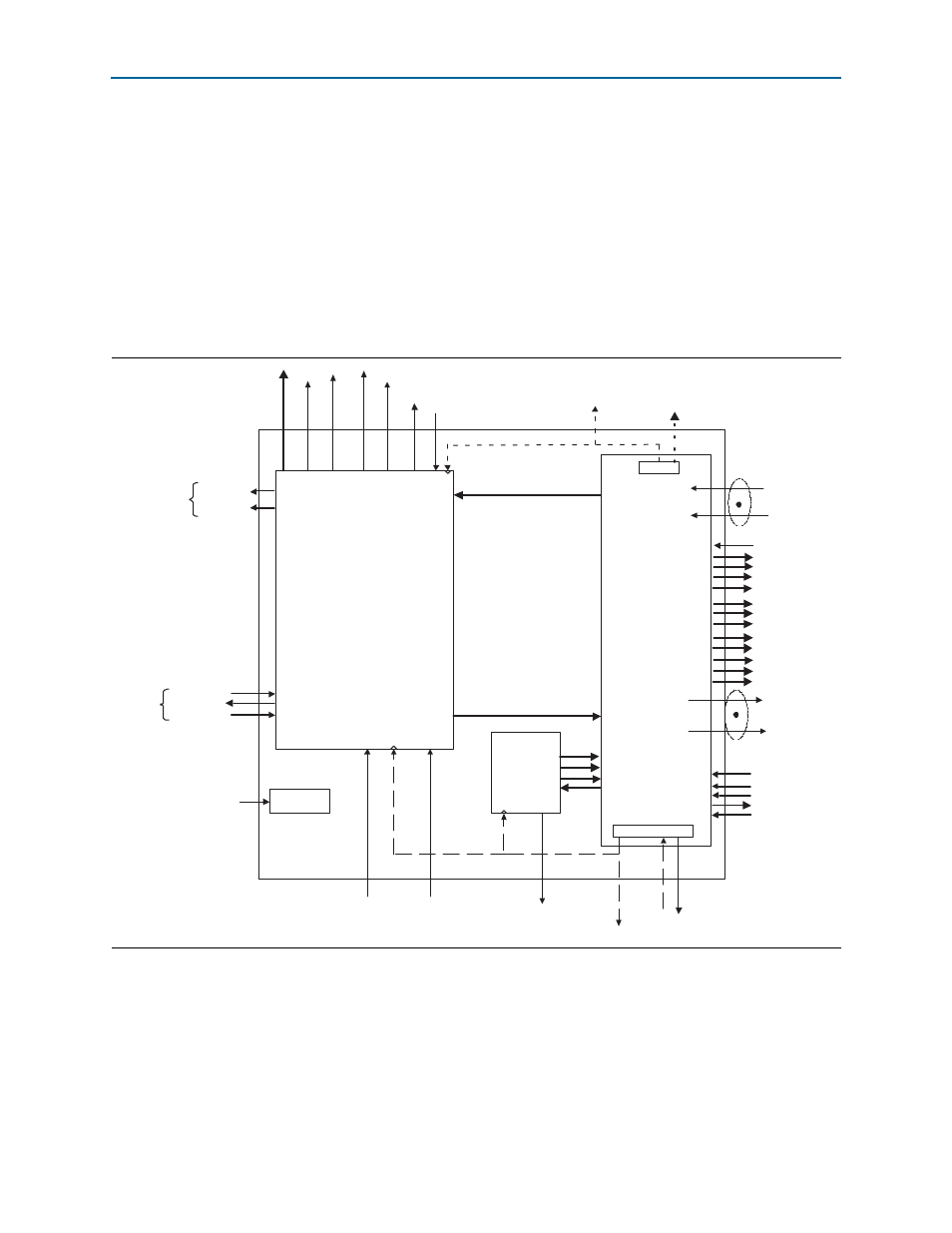

Arria ii gx/stratix iv phy layer, Transmitter link layer, Receiver layer with no fifo – Altera SerialLite II IP Core User Manual

Page 68: Figure 4–13. arria ii gx/stratix iv phy layer, Slite2_top

4–14

Chapter 4: Functional Description

Clocks and Data Rates

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

Your SerialLite II MegaCore function design always contains a PHY layer, based on

the device you select. The link layer portions is present if the Data Type option is set

to Packets. The inclusion of receiver and transmitter components is determined by the

Port Type

option that you select (Bidirectional, Transmitter only, Receiver only). For

example, if Data Type is Packets; Port Type is Bidirectional; the receiver FIFO is set to

0

bytes; and the device family is Stratix II GX, refer to the following diagrams:

■

Arria II GX/Stratix IV PHY Layer

■

■

Figure 4–13. Arria II GX/Stratix IV PHY Layer

slite2_top

mreset_n

reset_syncer

reset_logic_gx

slite2_phy

rx_clkout[0]

tx_coreclock

xcvr2

OR

xcvr2_tx/

xcvr2_rx

trefclk

txout[0]

txout[n]

rxin[0]

rxin[n]

TXPLL

stat_tc_pll_locked

RXPLL

err_rr_8berrdet

err_rr_disp

err_rr_rlv

stat_rr_sigdet

stat_rr_rxlocked

stat_rr_freqlock

stat_rr_pattdet

ctrl_tc_serial_lpbena

stat_rr_gxsync

txrdp_ena

txrdp_dav

txrdp_dat

Atlantic

Interface

rxrdp_dat

Atlantic

Interface

rxrdp_ena

tx_coreclock

rrefclk

stat_rr_link

ctrl_rr_enadscram

ctrl_tc_enascram

ctrl_tc_force_train

rcvd_clk_out

stat_tc_rst_done

err_rr_pol_r

e

v

_re

q

uired

err_rr_dskfi

fo_ofl

w

stat_rr_dsk

w

_d

one_bc

cal_blk_clk

reconfig_clk

reconfig_togxb

reconfig_fromgxb

err_rr_pcfifo_uflw

err_rr_pcfifo_oflw

err_tc_pcfifo_oflw

err_tc_pcfifo_uflw

err_rr_

foffre_ofl

w

stat_tc_

foffre_empty

gxb_powerdown