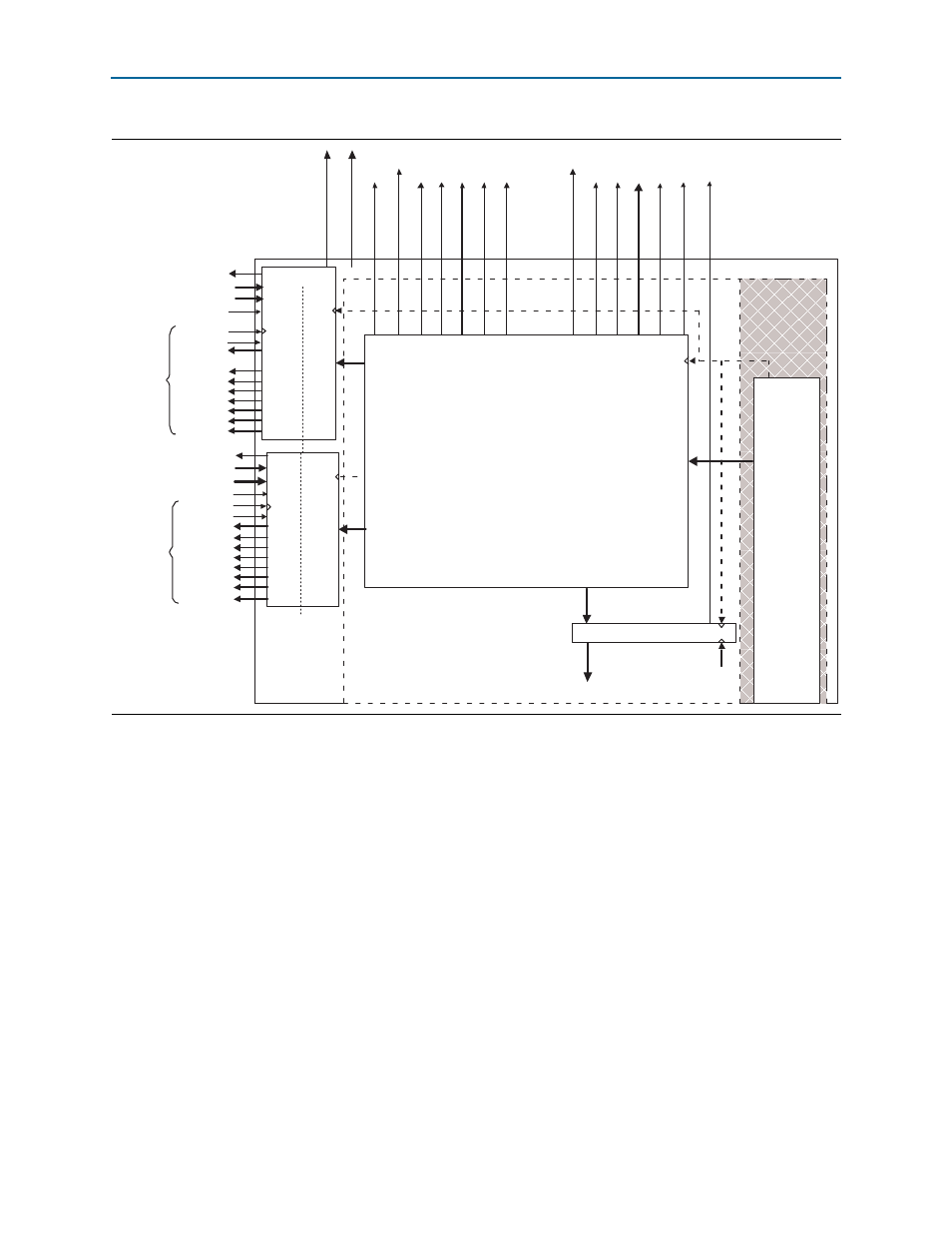

Receiver link layer with fifo, Figure 4–15. receiver link layer with fifo – Altera SerialLite II IP Core User Manual

Page 70

4–16

Chapter 4: Functional Description

Clocks and Data Rates

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

Figure 4–15. Receiver Link Layer With FIFO

slite2_top

high speed front

end (Phy)

slite2_ll

RX Core

Regular Data

Port Atlantic

FIFO

(rxrdp_atltop)

rxrdp_ena

rxrdp_dav

rxrdp_sop

rxrdp_eop

rxrdp_err

rxrdp_mty

rxrdp_dat

rxrdp_adr

Atlantic

Interface

(Reg Data

Packets )

rxrdp_clk

ctrl_rr_rdp_fcthresh

Phy Layer

Blocks (Ex

xcvr,

slite2_phy)

rxrdp_val

High Priority

Port Atlantic

FIFO

(rxhpp_atltop)

rxhpp_ena

rxhpp_dav

rxhpp_sop

rxhpp_eop

rxhpp_err

rxhpp_mty

rxhpp_dat

rxhpp_adr

Atlantic

Interface

(Priority

Packets )

rxhpp_clk

ctrl_rr_hpp_fcthresh

stat_rxhpp_empty

rxhpp_val

rrefclk

tx_coreclock

ctl_rxhpp_ftl

ctl_rxhpp_eopdav

stat_rxrdp_empty

ctl_rxrdp_ftl

ctl_rxrdp_eopdav

err_tc/rr_rxrdp_ofl

w

err_tc/rr_rxhpp_ofl

w

err_rr_f

of

fre_ofl

w

stat_tc_f

of

fre_empty

stat_rr_ebprx

err_rr_bip8

err_rr_crc

err_rr_in

v

alid_lmprx

err_rr_missing_star

t_dc

w

err_rr_addr_mismatch

err_rr_rx2txfif

o_ofl

w

stat_rr_fc_rdp_

v

alid

stat_rr_fc_hpp_

v

alid

stat_rr_fc_

v

alue

stat_rr_roe_ac

k

stat_rr_roe_nac

k

rx2tx_retimer_fifo

To TX Core