Altera SerialLite II IP Core User Manual

Page 81

Chapter 4: Functional Description

4–27

Signals

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

shows the Atlantic interface signals for streaming mode.

shows the protocol processor’s error, status, and control signals.

txhpp_err

Input

txhpp_clk

Error indicator on the Atlantic interface.

txhpp_mty[

tm-1:0]

Input

txhpp_clk

Number of empty bytes in the data word.

txhpp_dat[

td-1:0]

Input

txhpp_clk

User data bits.

txhpp_adr[3:0]

Input

txhpp_clk

User-defined packet ID.

Notes to

(1) In broadcast mode, these signals will have the corresponding receiver function number post-fixed. For example, err_rr_crc0 is the CRC error

signal from SerialLite II receiver block 0.

(2) m is the empty value, which is log2 (data width).

(3) d is the data width, which is 8 × transfer size × the RX number of lanes.

(4) tm is the empty value, which is log2 (data width).

(5) td is the data width, which is 8 × transfer size × the TX number of lanes.

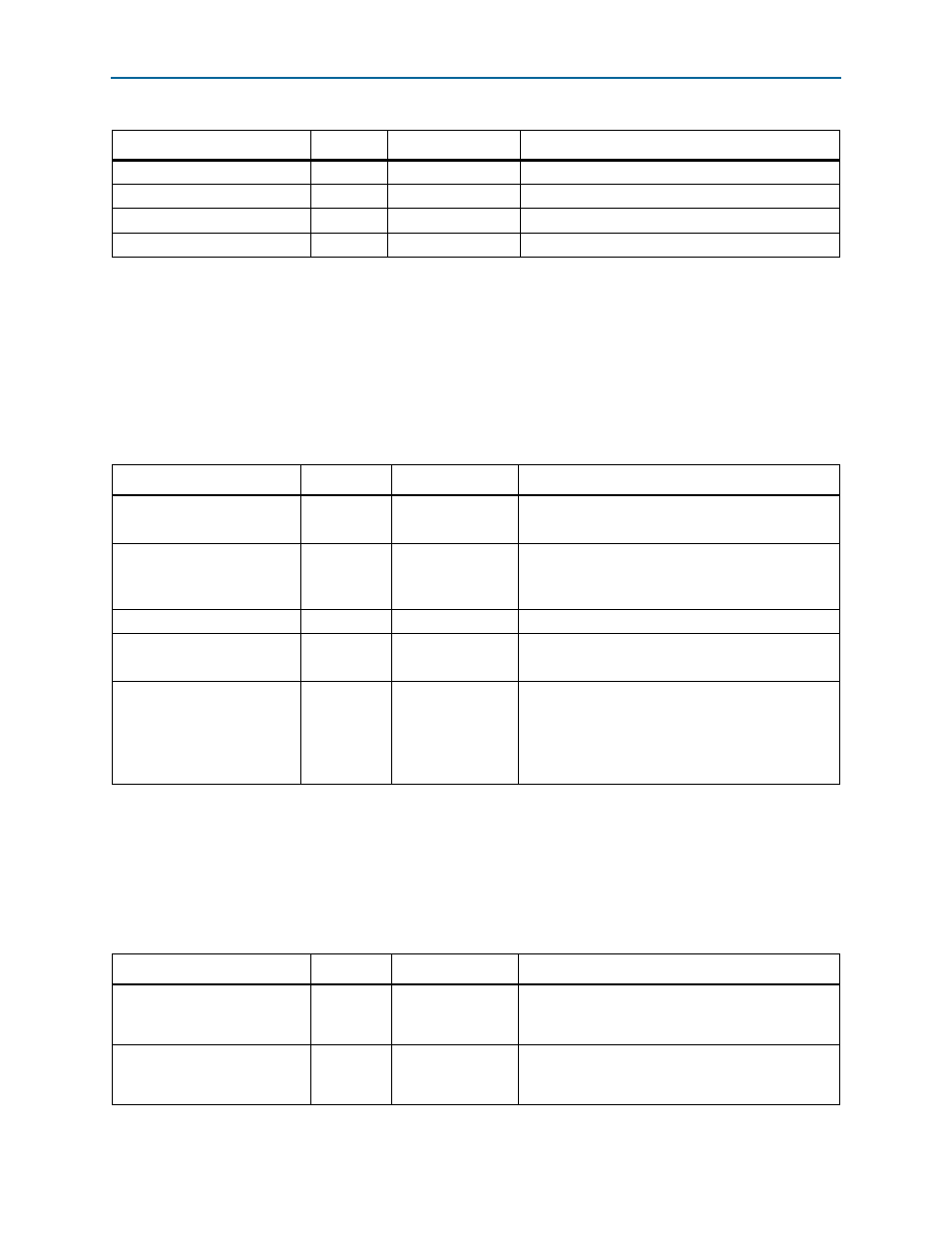

Table 4–7. Atlantic Interface Signals (Part 3 of 3)

Signal

Direction

Clock Domain

Description

Table 4–8. Atlantic Interface Signals for Streaming Mode

Signal

Direction

Clock Domain

Description

rxrdp_dat [d-1:0]

Output

rrefclk

Received user data bits.

rxrdp_ena

Output

rrefclk

Enable signal on the Atlantic interface.

Indicates that the data is valid on the current clock

cycle.

txrdp_dat [td-1:0]

Input

tx_coreclock

User data bits to be transmitted.

txrdp_ena

Input

tx_coreclock

Enable signal on the Atlantic interface.

Indicates that the data is valid.

txrdp_dav

Output

tx_coreclock

Indicates that the core is requesting the user data to

stop while the core inserts the clock compensation

sequence.

If Clock Compensation is not enabled, this signal will

always be high while the link is up.

Notes to

(1) In broadcast mode, these signals will have the corresponding receiver function number post-fixed. For example, err_rr_crc0 is the CRC error

signal from SerialLite II receiver block 0.

(2) n is = FIFO SIZE / (TSIZE * RX Number of Lanes).

(3) tn is = FIFO SIZE / (TSIZE * TX Number of Lanes).

Table 4–9. Protocol Processor’s Error, Status and Control Signals (Part 1 of 2)

Signal

Direction

Clock Domain

Description

err_rr_rxrdp_oflw

Output

rrefclk

Indicates that the Atlantic FIFO buffer has overflowed

and data has been lost when Clock Compensation is

disabled (regular data port).

err_rr_rxhpp_oflw

Output

rrefclk

Indicates that the Atlantic FIFO buffer has overflowed

and data has been lost when Clock Compensation is

disabled (priority data port).