Altera SerialLite II IP Core User Manual

Page 11

1–6

Chapter 1: About This MegaCore Function

Performance and Resource Utilization

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

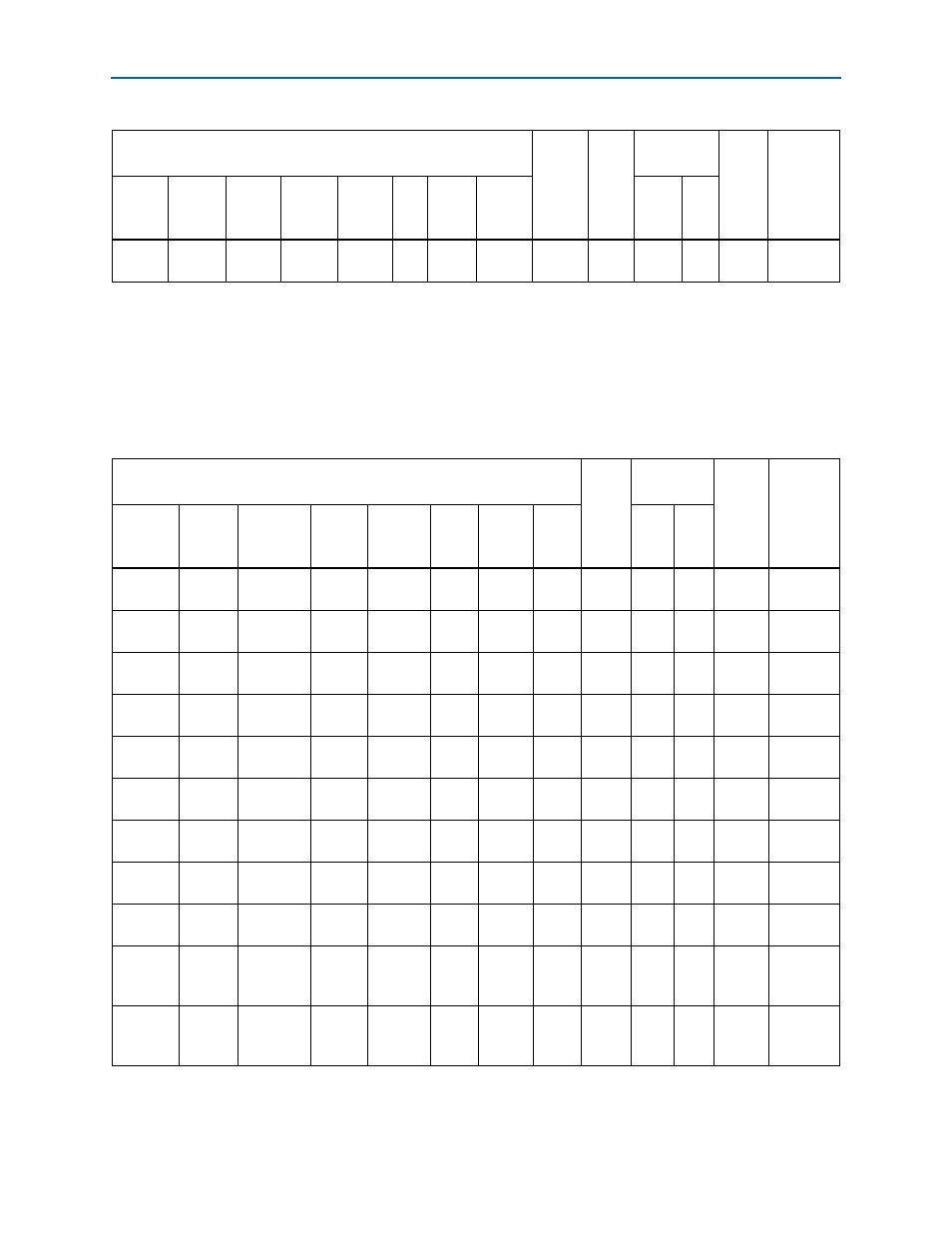

lists the resources and internal core speeds for a selection of variations using

1,024-byte FIFO buffers. These results were obtained using the Quartus II software

version 10.1 for the following device: Stratix GX (EP1SGX40GF1020C5).

Full-

Duplex

4

Packet

Priority

4

16

Yes

Yes

3528

2110

17

41

160

6375

Notes to

(1) A transfer size of 1 is used for 1,250 Mbps, 2 is used for 3,125 Mbps, and 4 is used for 6,375 Mbps.

(2) Total throughput equals the value in the Throughput column multiplied by the value in the Number of Lanes column.

Table 1–3. Performance for Stratix II GX (Part 2 of 2)

Parameters

Combi

n-

ational

ALUTs

Logic

Reg.

Memory

Blocks

f

MAX

(MHz)

Throughp

ut

Mbps

(2)

Data

Flow

Numbe

r of

Lanes

Data/

Type

Packet

Type

Transf

er Size

(1)

CR

C

Flow

Contr

ol

Retry-

on-

Error

M512

M4

K

Table 1–4. Performance for Stratix GX (Part 1 of 3)

Parameters

LEs

Memory

Blocks

f

MAX

(MHz)

Throughp

ut

Data

Flow

Number

of

Lanes

Data Type

Packet

Type

Transfer

CRC

Flow

Contro

l

Retry

- on-

Error

M51

2

M4K

Full-

Duplex

1

Packet

Data

1

No

No

No

1065

9

10

178

1250

Full-

Duplex

1

Packet

Data

2

No

No

No

1098

0

11

182

3125

Full-

Duplex

4

Packet

Data

1

No

No

No

1711

15

11

186

1250

Full-

Duplex

4

Packet

Data

2

No

No

No

2706

23

22

180

3125

Full-

Duplex

16

Packet

Data

2

No

No

No

8328

50

87

158

3125

Full-

Duplex

1

Packet

Data

1

32

Yes

No

1687

10

10

172

1250

Full-

Duplex

1

Packet

Data

2

32

Yes

No

1728

2

11

163

3125

Full-

Duplex

4

Packet

Data

1

32

Yes

No

2496

17

11

151

1250

Full-

Duplex

4

Packet

Data

2

32

Yes

No

3848

25

22

127

3125

Full-

Duplex

1

Packet

Data

and

Priority

2

No

Both

No

2169

2

19

181

3125

Full-

Duplex

1

Packet

Data

and

Priority

2

32

Both

No

2538

2

19

165

3125