Altera SerialLite II IP Core User Manual

Page 90

5–4

Chapter 5: Testbench

Testbench Specifications

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

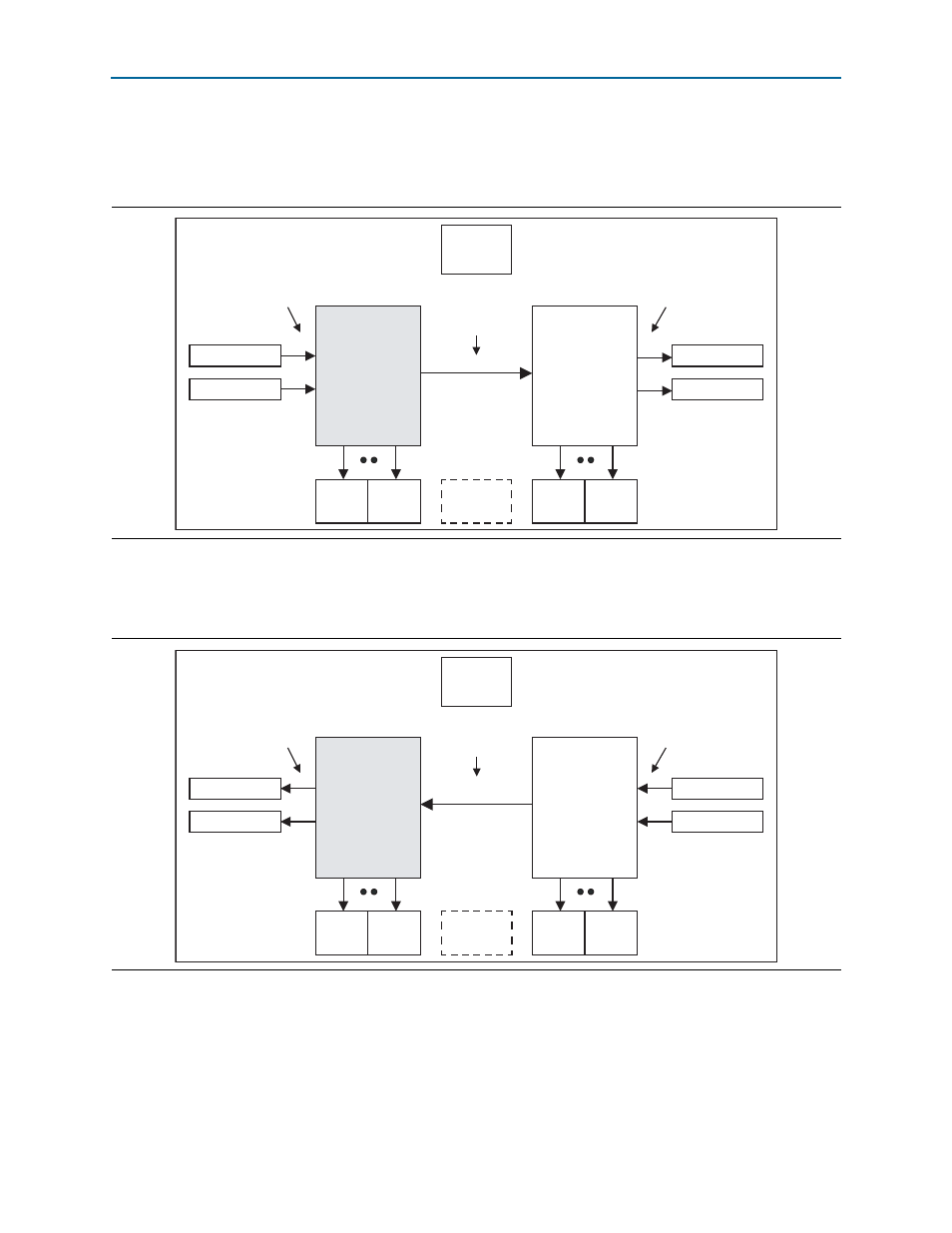

shows the testbench environment for a SerialLite II single

mode–transmitter only, non-broadcast MegaCore function. The SISTER model

contains a receiver.

shows the testbench environment for a SerialLite II single mode–receiver

only, non-broadcast MegaCore function. The SISTER model contains a transmitter.

Figure 5–2. SerialLite II Testbench Environment (Single Mode–Transmitter Only, Verilog HDL Only, Non-Broadcast)

sl2_top

(IP Functional

Simulation Model)

DUT

sl2_top_sister

(IP Functional

Simulation Model)

SISTER

AGEN_DAT_DUT

Atlantic

Interface

Atlantic

Interface

SerialLite II

High-Speed

Interface

SerialLite II Testbench

AGEN_PRI_DUT

AMON_DAT_SIS

AMON_PRI_SIS

Clock and

Reset

Generator

Status

Monitor 1

(SISTER)

Status

Monitor X

(SISTER)

Status

Monitor 1

(DUT)

Status

Monitor X

(DUT)

Custom

PHY IP

Core

Figure 5–3. SerialLite II Testbench Environment (Single Mode–Receiver Only, Verilog HDL Only, Non-Broadcast)

sl2_top

(IP Functional

Simulation Model)

DUT

sl2_top_sister

(IP Functional

Simulation Model)

SISTER

Atlantic

Interface

Atlantic

Interface

SerialLite II

High-Speed

Interface

SerialLite II Testbench

AMON_DAT_DUT

AMON_PRI_DUT

AGEN_DAT_SIS

AGEN_PRI_SIS

Clock and

Reset

Generator

Status

Monitor 1

(SISTER)

Status

Monitor X

(SISTER)

Status

Monitor 1

(DUT)

Status

Monitor X

(DUT)

Custom

PHY IP

Core