Altera SerialLite II IP Core User Manual

Page 82

4–28

Chapter 4: Functional Description

Signals

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

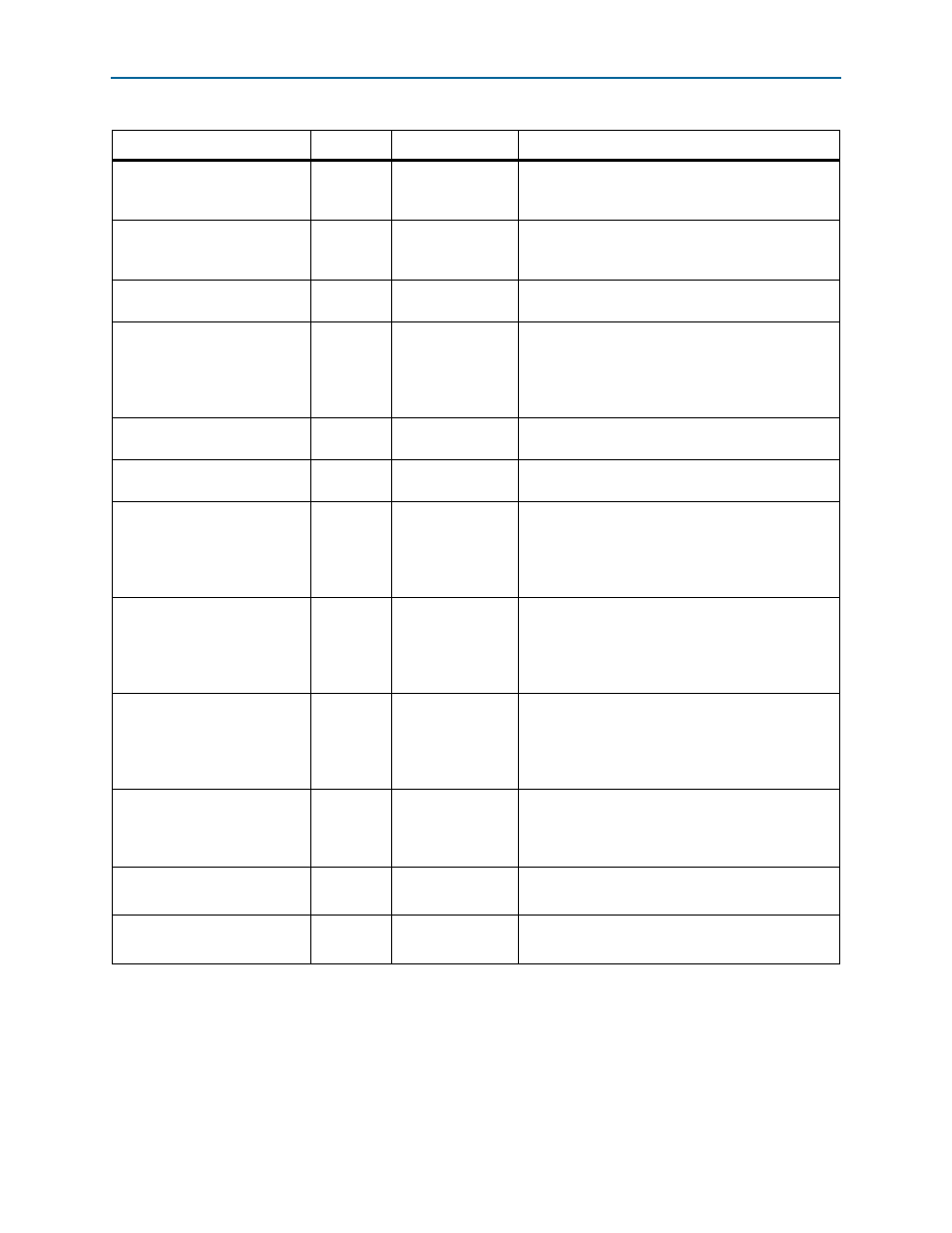

err_tc_rxrdp_oflw

Output

tx_coreclock

Indicates that the Atlantic FIFO buffer has overflowed

and data has been lost when Clock compensation is

enabled (regular data port).

err_tc_rxhpp_oflw

Output

tx_coreclock

Indicates that the Atlantic FIFO buffer has overflowed

and data has been lost when the Clock

Compensation is enabled (priority data port).

err_txrdp_oflw

Output

txrdp_clk

Indicates that the Atlantic FIFO buffer has overflowed

and data has been lost (regular data port).

err_txhpp_oflw

Output

txhpp_clk

Indicates that the high-priority Atlantic FIFO buffer

has overflowed and data has been lost. If the Retry-

on-error parameter is turned on, this signal remains

high until the FIFO buffer has been emptied by the

SerialLite II MegaCore function.

stat_rxrdp_empty

Output

rxdrp_clk

Indicates that the internal Atlantic FIFO buffer is

empty, and the read request is ignored.

stat_rxhpp_empty

Output

rxhpp_clk

Indicates that the internal Atlantic FIFO buffer is

empty, and the read request is ignored.

ctl_rxhpp_ftl

[

n-1:0]

Input

rxhpp_clk

Receive high priority port FIFO threshold low (dav

control). Determines when to inform the user logic

that data is available via the rxhpp_dav signal. This

threshold applies to all buffers. Units are in elements.

Only change at reset.

ctl_rxrdp_ftl

[

n-1:0]

Input

rxrdp_clk

Receive regular data port FIFO threshold low (dav

control). Determines when to inform the user logic

that space is available via the rxrdp_dav signal. This

threshold applies to all buffers. Units are in elements.

Only change at reset.

ctl_rxhpp_eopdav

Input

rxhpp_clk

Receive high priority port FIFO buffer end-of-packet

(EOP)-based dav control. Assert to turn on dav when

there is an end of packet below the FTL threshold.

Value applies to all Atlantic buffers. Only change at

reset.

ctl_rxrdp_eopdav

Input

rxrdp_clk

Receive regular data port FIFO buffer EOP-based dav

control. Assert to turn on dav when there is an end of

packet below the FTL threshold. Value applies to all

Atlantic buffers. Only change at reset.

ctl_txhpp_fth

[tn-1:0]

Input

txhpp_clk

Transmit high priority port FIFO buffer threshold high

dav

control.

ctl_txrdp_fth

[

tn-1:0]

Input

txrdp_clk

Transmit regular data port FIFO buffer threshold high

dav

control.

Notes to

(1) In broadcast mode, these signals will have the corresponding receiver function number post-fixed. For example, err_rr_crc0 is the CRC error

signal from SerialLite II receiver block 0.

(2) n is = FIFO SIZE / (TSIZE * RX Number of Lanes).

(3) tn is = FIFO SIZE / (TSIZE * TX Number of Lanes).

Table 4–9. Protocol Processor’s Error, Status and Control Signals (Part 2 of 2)

Signal

Direction

Clock Domain

Description