Own in, Genera – Altera SerialLite II IP Core User Manual

Page 89

Chapter 5: Testbench

5–3

Testbench Specifications

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

■

The generated data follows a pseudo-random sequence (Verilog HDL) or

incrementing data sequence (VHDL) that is checked by the Atlantic monitors.

■

Each packet has an incrementing identifier (first byte in the packet) that is checked

by the Atlantic monitor.

The SISTER MegaCore function is a SerialLite II MegaCore function with parameters

derived from the DUT parameters. If the DUT is symmetrical (receiver's parameters

matching transmitter's parameters), the SISTER's parameters match the DUT

parameters. If the DUT is asymmetrical, the SISTER's parameters are different than

the DUT's parameters, so that the DUT's transmitter parameters match the SISTER's

receiver parameters and vice-versa. For a broadcast DUT, there are multiple SISTER

instantiations. Pin monitor utilities monitor the SerialLite II status and error pins of

the DUT and SISTER(s).

1

The Custom PHY IP core is only applicable in configurations targeted for Arria V and

Stratix V devices.

Depending on the SerialLite II link variation you choose (for example, using the

single, broadcast, or asymmetric mode) the SerialLite II testbench environment may

change, but the basic functionality is unchanged: data is sent or received on the

Atlantic interface of the SerialLite II DUT IP model and received or sent on the

Atlantic interface of the SerialLite II SISTER IP model.

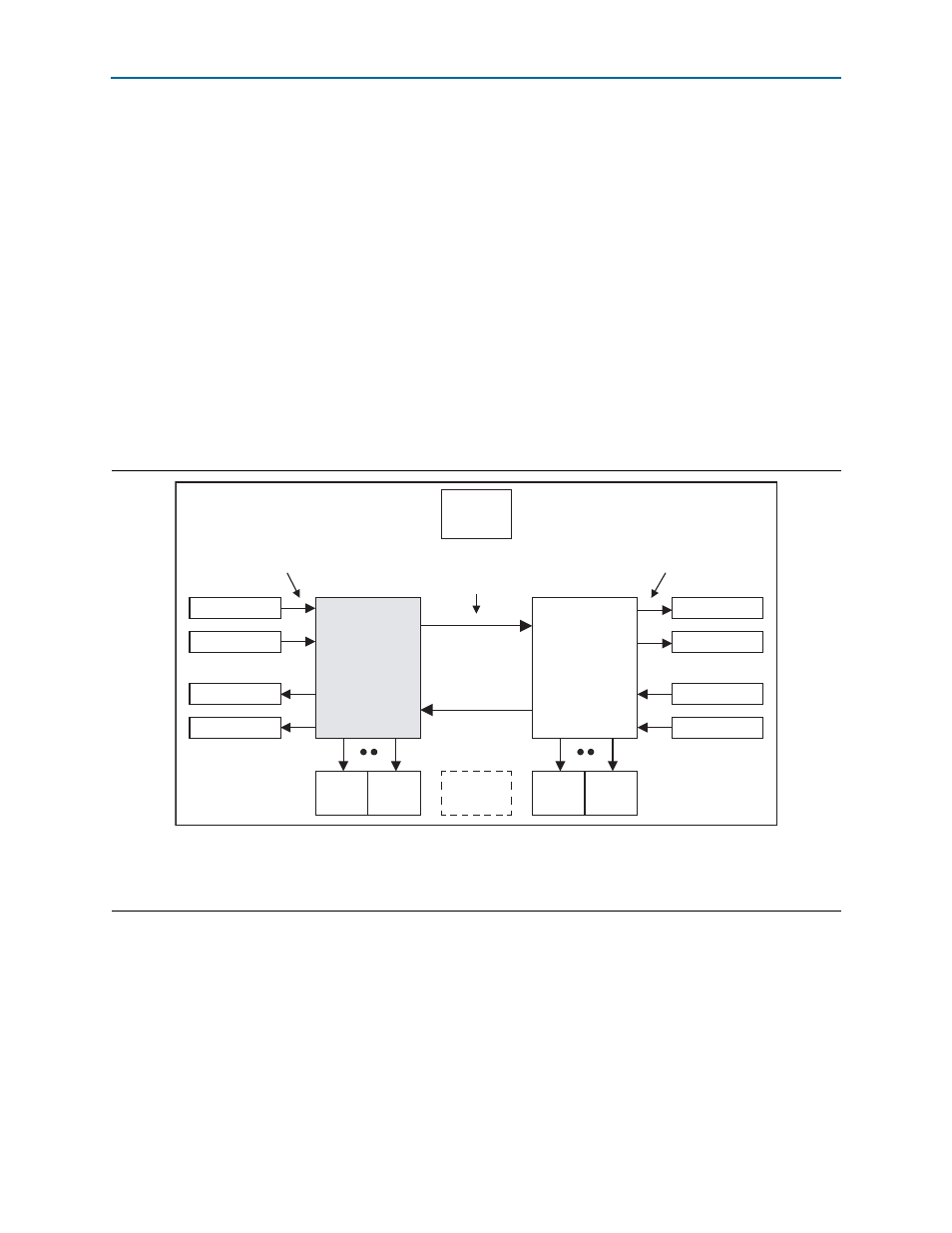

Figure 5–1. SerialLite II Testbench Environment (Non-Broadcast)

Notes to

(1) The DUT and the SISTER MegaCore functions may have different parameters; depending on the DUT parameters, and some components may be

missing.

(2) _DAT = Regular Data Port; _PRI = High Priority Port; _DUT = Refers to DUT side; _SIS = Refers to SISTER side.

sl2_top

(IP Functional

Simulation Model)

DUT

sl2_top_sister

(IP Functional

Simulation Model)

SISTER

AGEN_DAT_DUT

Status

Monitor 1

(DUT)

Clock and

Reset

Generator

Custom

PHY IP

Core

Atlantic

Interface

Atlantic

Interface

SerialLite II

High-Speed

Interface

SerialLite II Testbench

AGEN_PRI_DUT

AMON_DAT_DUT

AMON_PRI_DUT

AMON_DAT_SIS

AMON_PRI_SIS

AGEN_DAT_SIS

AGEN_PRI_SIS

Status

Monitor X

(DUT)

Status

Monitor 1

(SISTER)

Status

Monitor X

(SISTER)