3 adc x input select, 24 hpf control (address 1bh), 1 adcx high-pass filter – Cirrus Logic CS42L56 User Manual

Page 74: 2 adcx high-pass filter freeze, 3 hpf x corner frequency, Register, P 75, Cs42l56

74

DS851F2

CS42L56

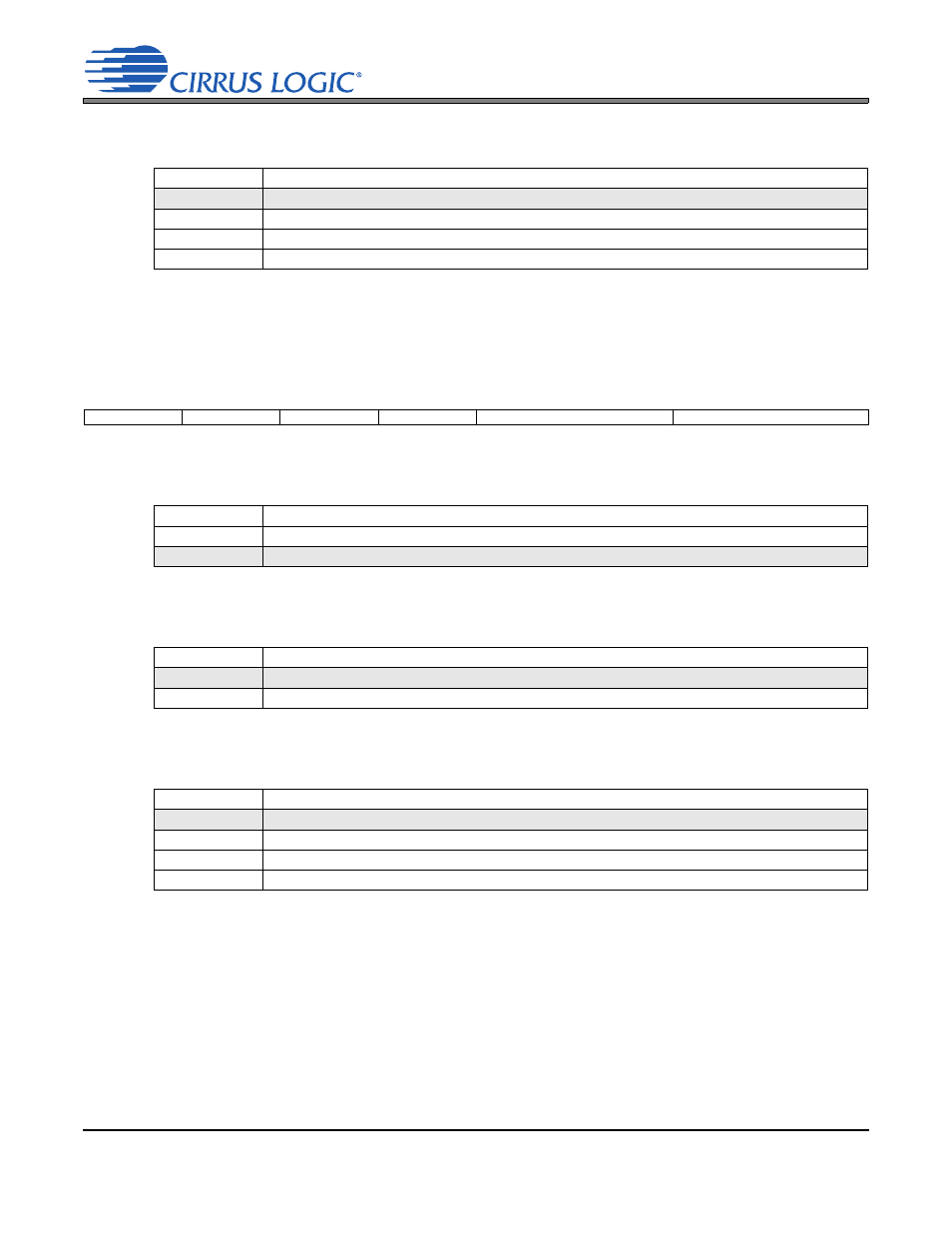

6.23.3 ADC x Input Select

Selects the specified analog input signal into ADCx.

Note:

Pseudo-differential inputs are not available when the PGA is bypassed. Use the AINx_REF bits

Analog Input 1 x Reference Configuration

and

“Analog Input 1 x Reference Configuration” on page 74

)

to properly configure the input channel.

6.24 HPF Control (Address 1Bh)

6.24.1 ADCx High-Pass Filter

Configures the internal high-pass filter after ADCx.

6.24.2 ADCx High-Pass Filter Freeze

Configures the high pass filter’s digital DC subtraction and/or calibration after ADCx.

6.24.3 HPF x Corner Frequency

Sets the corner frequency (-3 dB point) for the internal High-Pass Filter (HPF).

ADCxMUX[1:0]

Selected Input to ADCx

00

PGAx - Use PGAxMUX bit (

“PGA x Input Select” on page 77

) to select an input channel.

01

AIN1x; PGA is bypassed.

10

AIN2x; PGA is bypassed.

11

AIN3x; PGA is bypassed.

7

6

5

4

3

2

1

0

HPFB

HPFRZB

HPFA

HPFRZA

HPFB_CF1

HPFB_CF0

HPFA_CF1

HPFA_CF0

HPFx

High Pass Filter Status

0

Disabled

1

Enabled

HPFRZx

High Pass Filter Digital Subtraction

0

Continuous DC Subtraction

1

Frozen DC Subtraction

HPFx_CF[1:0]

HPF Corner Frequency Setting (Fs=48 kHz)

00

1.8 Hz

01

119 Hz

10

236 Hz

11

464 Hz