2 clock ratio, 7 serial format (address 07h), 1 codec digital interface format – Cirrus Logic CS42L56 User Manual

Page 61: P 62, Cs42l56

DS851F2

61

CS42L56

6.6.2

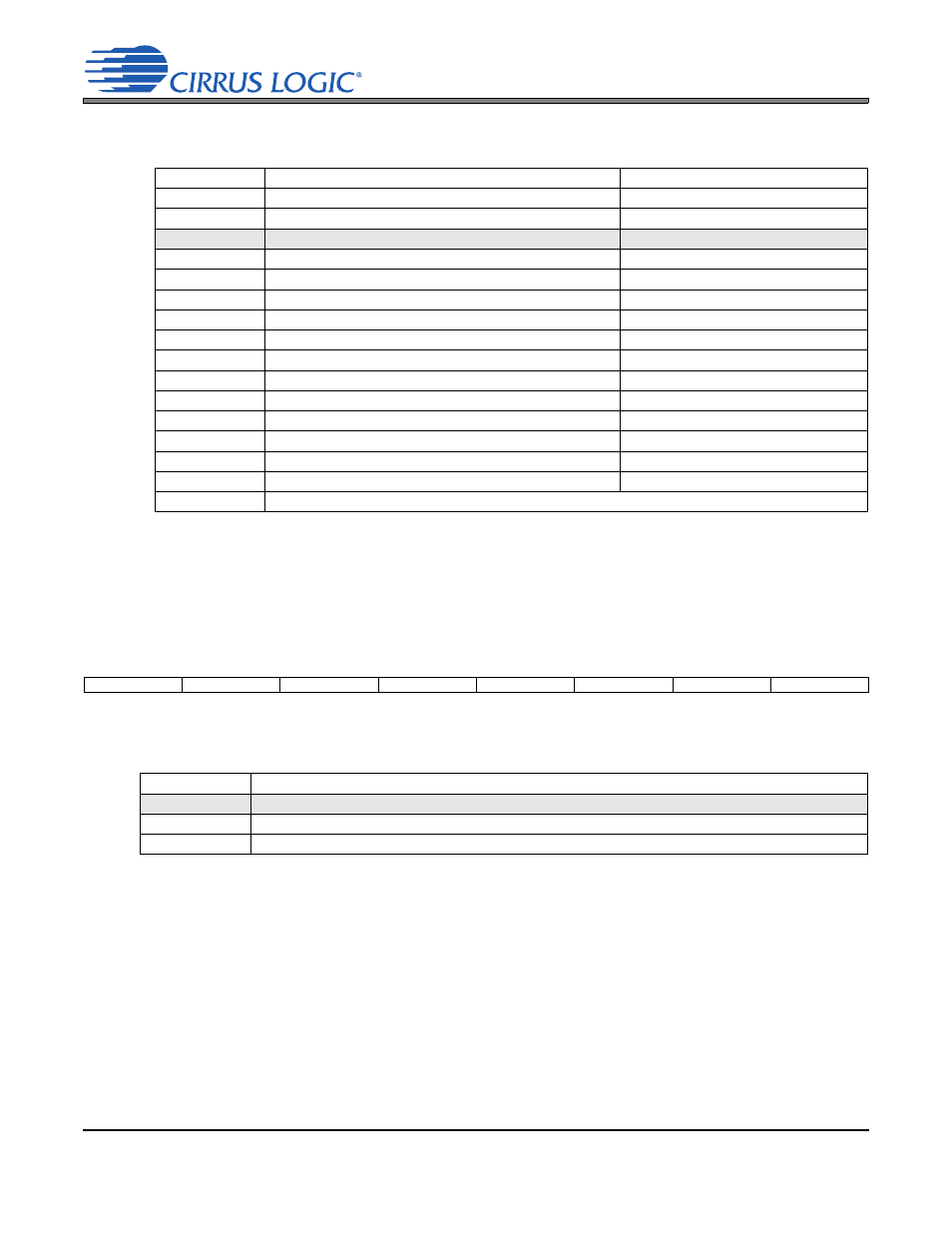

Clock Ratio

Configures the appropriate internal MCLK divide ratio for LRCK and SCLK.

Notes:

1. Register settings not shown in the table are reserved. Use

Table 3. “Serial Port Clock Ratio Settings”

for determining the register settings based on the system master clock (MCLK),

bit clock (SCLK) and frame clock (LRCK) frequencies.

6.7

Serial Format (Address 07h)

6.7.1

CODEC Digital Interface Format

Configures the digital interface format for data on SDOUT and SDIN.

RATIO[4:0]

MCLK/LRCK Ratio

MCLK/SCLK Ratio

01000

128

2

01001

125

2

01011

136

2

01100

192

3

01101

187.5

3

10000

256

4

10001

250

4

10011

272

4

10100

384

6

10101

375

6

11000

512

8

11001

500

8

11011

544

8

11100

750

12

11101

768

12

Application:

“Serial Port Clocking” on page 47

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

DIF

Reserved

Reserved

Reserved

DIF

CODEC Interface Format

0

I²S

1

Left Justified

Application:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)