Figure 30. peak detect & limiter, 8 serial port clocking, Table 3. serial port clock ratio settings – Cirrus Logic CS42L56 User Manual

Page 46: Figure 30.peak detect & limiter, Serial port clocking, Cs42l56

46

DS851F2

CS42L56

4.8

Serial Port Clocking

The CODEC serial audio interface port operates either as a slave or master. It accepts externally generated

clocks in Slave Mode (M/S = 0b) and will generate synchronous clocks derived from an input master clock

(MCLK) in Master Mode (M/S = 1b). The RATIO[4:0] bits need to be set appropriately according to the

clocks being used in the system for correct device functionality.

Table 3. “Serial Port Clock Ratio Settings”

shows possible clock frequencies achievable by the CS42L56 serial port and pro-

vides a reference on how the RATIO[4:0] bits need to be configured for different clock ratios.

shows how SCLK and LRCK are internally derived in Master Mode.

MCLK (MHz)

LRCK (kHz)

MCLK/ LRCK

Clock Ratio

SCLK (MHz)

MCLK/SCLK

Clock Ratio

RATIO[4:0]

22.5792

(MKPREDIV=1b)

(MCLKDIV2=1b)

11.0250

2048

0.7056

32

11000

22.0500

1024

1.4112

16

10000

44.1000

512

2.8224

8

01000

11.2896

(MKPREDIV=0b)

(MCLKDIV2=1b)

11.0250

1024

0.7056

16

11000

22.0500

512

1.4112

8

10000

44.1000

256

2.8224

4

01000

5.6448

(MKPREDIV=0b)

(MCLKDIV2=0b)

11.0250

512

0.7056

8

11000

22.0500

256

1.4112

4

10000

44.1000

128

2.8224

2

01000

Table 3. Serial Port Clock Ratio Settings

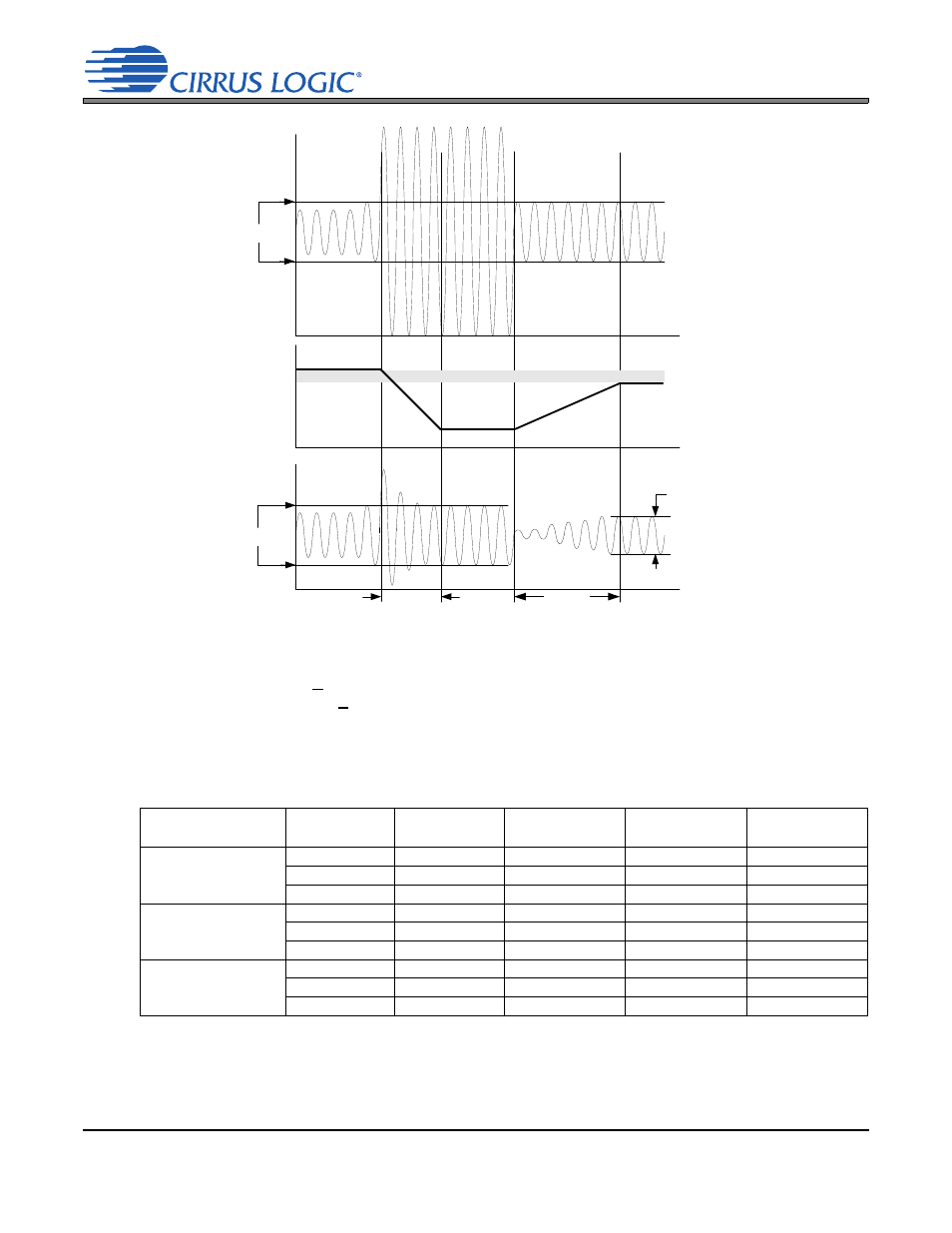

MAX[2:0]

Output

(after Limiter)

Input

RRATE[5:0]

ARATE[5:0]

Volume

Limiter

CUSH[2:0]

ATTACK/RELEASE SOUND

CUSHION

MAX[2:0]

Figure 30. Peak Detect & Limiter