5 mclk divide, 6 mclk disable, 6 clocking control 2 (address 06h) – Cirrus Logic CS42L56 User Manual

Page 60: 1 clock ratio auto-detect, 5 mclk divide 6.5.6 mclk disable, P 61, Cs42l56

60

DS851F2

CS42L56

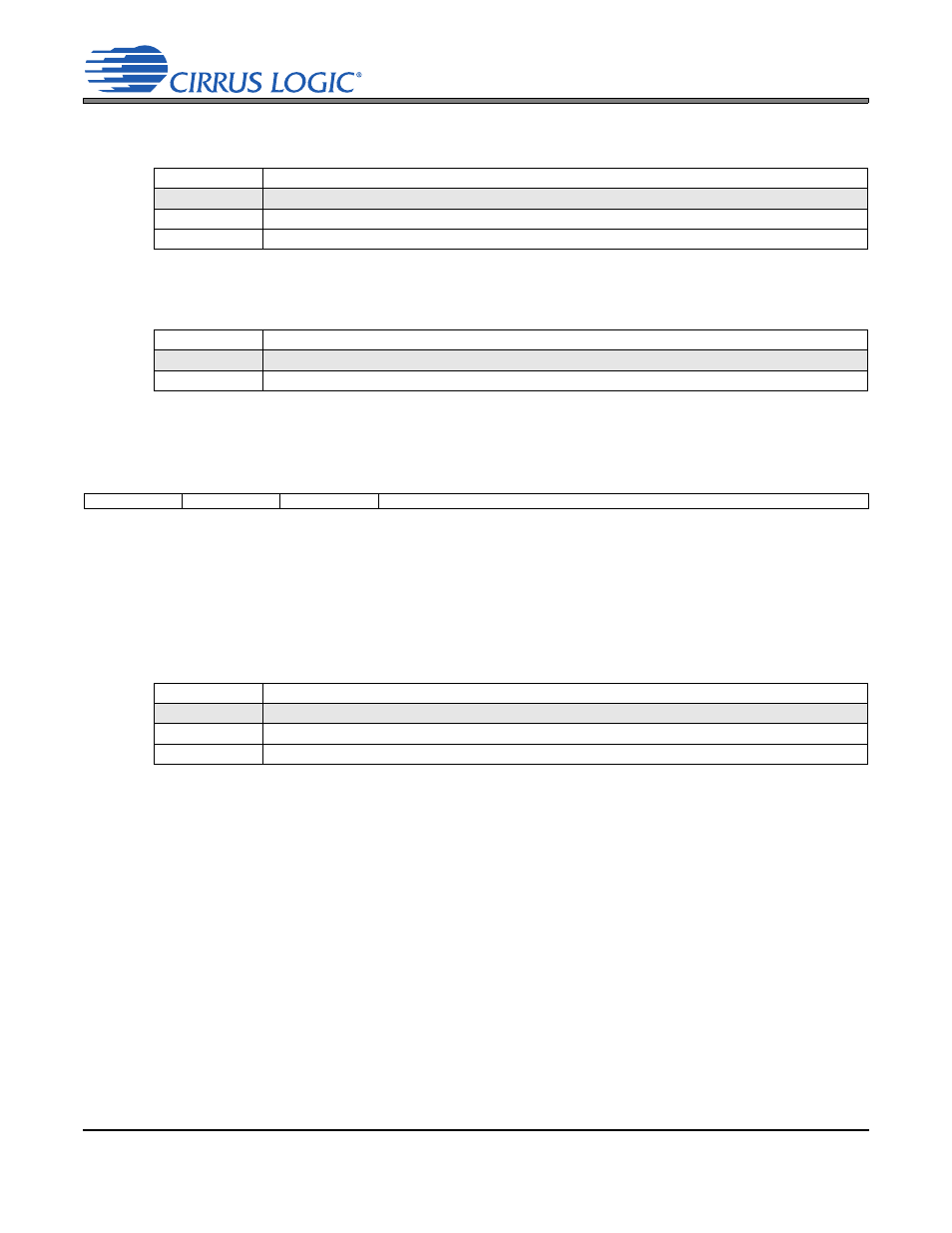

6.5.5

MCLK Divide

Configures a divide of the MCLK after the MCLK pre-divide.

6.5.6

MCLK Disable

Configures the MCLK signal prior to all internal circuitry.

Note:

This function should be enabled during power down (PDN=1) ONLY.

6.6

Clocking Control 2 (Address 06h)

6.6.1

Clock Ratio Auto-Detect

Configures the power status of the Auto-Detect circuitry. When enabled, the Auto-Detect circuitry detects

when the LRCK changes and automatically adjusts internal clock divide-ratios eliminating the need of a

register write to account for the change. It should be noted that the Auto-detect circuitry can only detect

when the LRCK changes by a factor of two while the MCLK stays the same (for instance, Mclk = 6.000

MHz; LRCK changes from 48 kHz to 24 kHz). Any other major clock frequency changes must be account-

ed for by appropriate control port writes.

Note:

When AUTO is enabled, the MCLK/LRCK ratio must be implemented according to

.

MCLKDIV2

MCLK signal into CODEC

0

No divide

1

Divided by 2

Application:

“Serial Port Clocking” on page 47

MCLKDIS

MCLK signal into CODEC

0

On

1

Off; Disables the clock tree to save power when the CODEC is powered down.

7

6

5

4

3

2

1

0

Reserved

Reserved

AUTO

RATIO4

RATIO3

RATIO2

RATIO1

RATIO0

AUTO

Auto-detection of Clock Ratio

0

Disabled

1 Enabled

Application: