Switching specifications - i²c control port, Figure 10. i²c control port timing, Figure 10.i²c control port timing – Cirrus Logic CS42L56 User Manual

Page 23

DS851F2

23

CS42L56

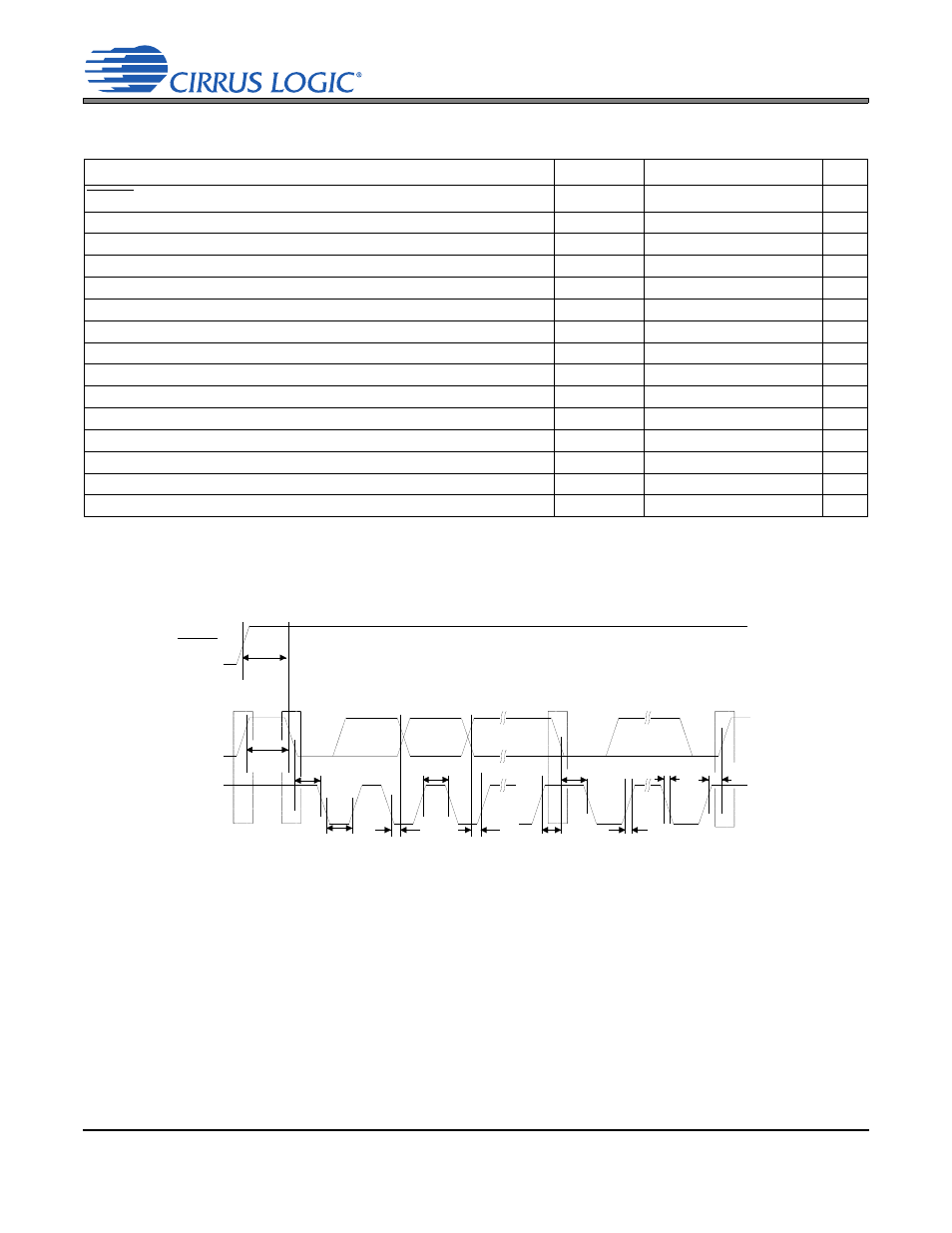

SWITCHING SPECIFICATIONS - I²C CONTROL PORT

Inputs: Logic 0 = GND = AGND, Logic 1 = VL

Notes:

22. All specifications are valid for the signals at the pins of the CS42L56 with the specified load capacitance.

23. Data must be held for sufficient time to bridge the transition time, t

f

, of SCL.

Parameter Symbol

Min

Max

Unit

RESET Rising Edge to Start

t

irs

500

-

ns

SCL Clock Frequency

f

scl

-

550

kHz

Start Condition Hold Time (prior to first clock pulse)

t

hdst

0.6

-

µs

Clock Low Time

t

low

1.3

-

µs

Clock High Time

t

high

0.6

-

µs

Setup Time for Repeated Start Condition

t

sust

0.6

-

µs

SDA Input Hold Time from SCL Falling

t

hddi

0

0.9

µs

SDA Output Hold Time from SCL Falling

t

hddo

0.2

0.9

µs

SDA Setup Time to SCL Rising

t

sud

100

-

ns

Rise Time of SCL and SDA

t

rc

-

300

ns

Fall Time SCL and SDA

t

fc

-

300

ns

Setup Time for Stop Condition

t

susp

0.6

-

µs

Bus Free Time Between Transmissions

t

buf

1.3

-

µs

SDA Bus Capacitance

C

L

-

400

pF

SDA Pull-Up Resistance

R

p

500

-

t buf

t hdst

t hdst

t

low

t r

t f

t

hdd

t high

t sud

t sust

t susp

Stop

Start

Start

Stop

Repeated

SDA

SCL

t irs

RESET

Figure 10. I²C Control Port Timing