Figure 31. serial port timing in master mode, Figure 31.serial port timing in master mode, Figure 31 – Cirrus Logic CS42L56 User Manual

Page 48: Cs42l56, Mclk

48

DS851F2

CS42L56

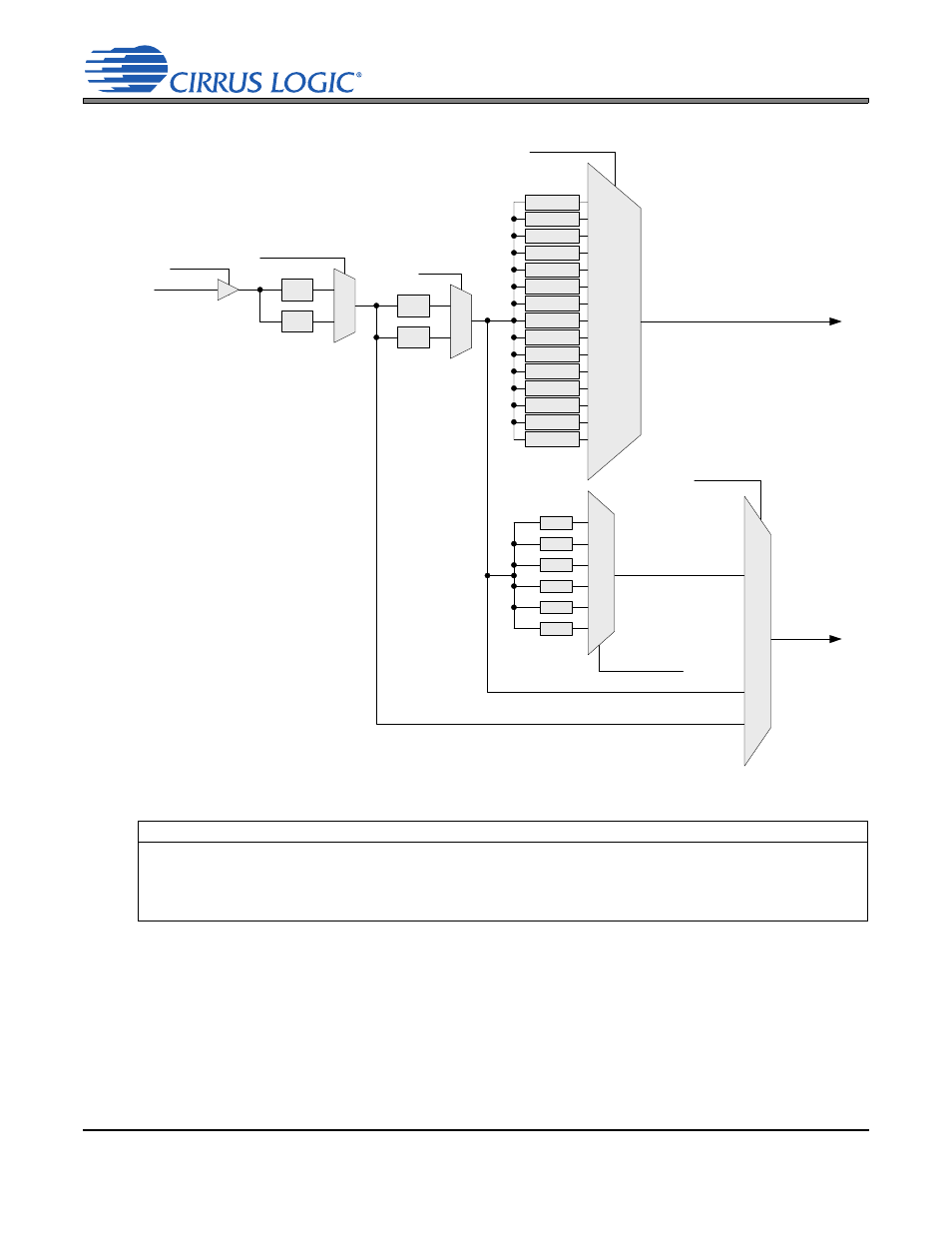

Referenced Control

Register Location

SCK=MCK[1:0] ....................

MKPREDIV...........................

MCLKDIV2...........................

MCLKDIS.............................

RATIO[4:0]...........................

“MCLK Divide” on page 61

“MCLK Disable” on page 61

“Clock Ratio” on page 62

SCK=MCK[1:0]

MCLK

2

1

MCLKPREDIV

0

1

MCLKDIS

2

1

MCLKDIV2

0

1

01001

01000

01011

01101

10001

01100

10000

10011

10101

10100

11001

11000

11011

11100

11101

RATIO[4:0]

125

128

136

187.5

192

250

256

272

375

384

500

512

544

750

768

LRCK

SCLK

010

011

100

101

110

111

00

10

11

RATIO[4:2]

NOTE:

The SCLK divide ratios shown in the figure are not

accurate when MCLK is a multiple of 6 MHz. For

accurate SCLK frequency values please refer to

Figure 31. Serial Port Timing in Master Mode

Table 3. “Serial Port Clock Ratio Settings” beginning on

page 47

and

.