System memory 3-dimm layout guidelines, System memory decoupling guidelines, Figure 39. system memory 3-dimm routing topologies – Intel 815 User Manual

Page 74: Table 19. system memory 3-dimm solution space, 74 intel, 815 chipset platform design guide

System Memory Design Guidelines

R

74

Intel

®

815 Chipset Platform Design Guide

6.3.2

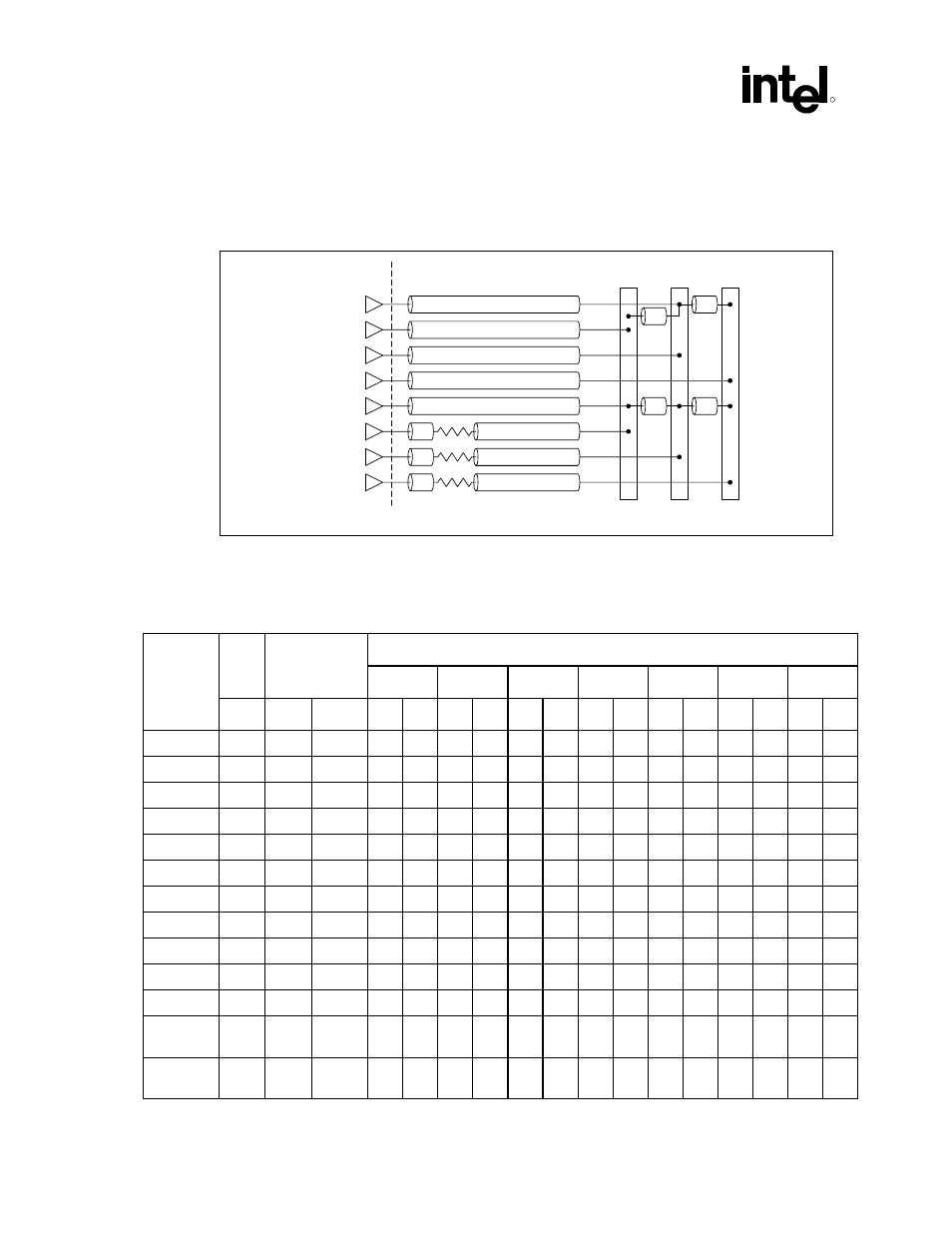

System Memory 3-DIMM Layout Guidelines

Figure 39. System Memory 3-DIMM Routing Topologies

Topology 1

82815

Topology 2

Topology 3

Topology 6

Topology 7

sys_mem_3DIMM_routing_topo

A

C

D

C

D

10

Ω

10

Ω

G

G

DIMM 0

DIMM 1

B

DIMM 2

B

Topology 4

E

Topology 5

F

Topology 8

E

10

Ω

G

B

B

In addition to meeting the spacing requirements outlined in Table 19, system memory signal trace

edges must be at least 30 mils from any other non-system memory signal trace edge.

Table 19. System Memory 3-DIMM Solution Space

Trace Lengths (inches)

Trace

(mils)

A B C D E F G

Signal

Top. Width Spacing Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

SCS[5:4]#

4 5 10

1

4.5

SCS[3:2]#

3 5 10 1

4.5

SCS[1:0]#

2 5 10 1

4.5

SMAA[7:4]

6 10 10 2 4

0.4

0.5

SMAB[7:4]# 7 10 10

2 4

0.4

0.5

SMAC[7:4}

8 10 10

2 4 0.4

0.5

SCKE[5:4]

4 10 10

3 4

SCKE[3:2]

3 10 10 3

4

SCKE[1:0]

2 10 10 3 4

SMD[63:0] 1

5 10

1.75

4

0.4

0.5

SDQM[7:0]

1

10

10

1.5 3.5 0.4 0.5

SCAS#,

SRAS#, SWE#

5

5

10

0.4

0.5

1 4

SBS[1:0],

SMAA[12:8,3:0]

5

5

10

0.4

0.5

1 4