3v/v5ref sequencing, Figure 78. 3.3v/v5ref sequencing circuitry, 3 3.3v/v5ref sequencing – Intel 815 User Manual

Page 154

Power Delivery

R

154

Intel

®

815 Chipset Platform Design Guide

12.4.3 3.3V/V5REF

Sequencing

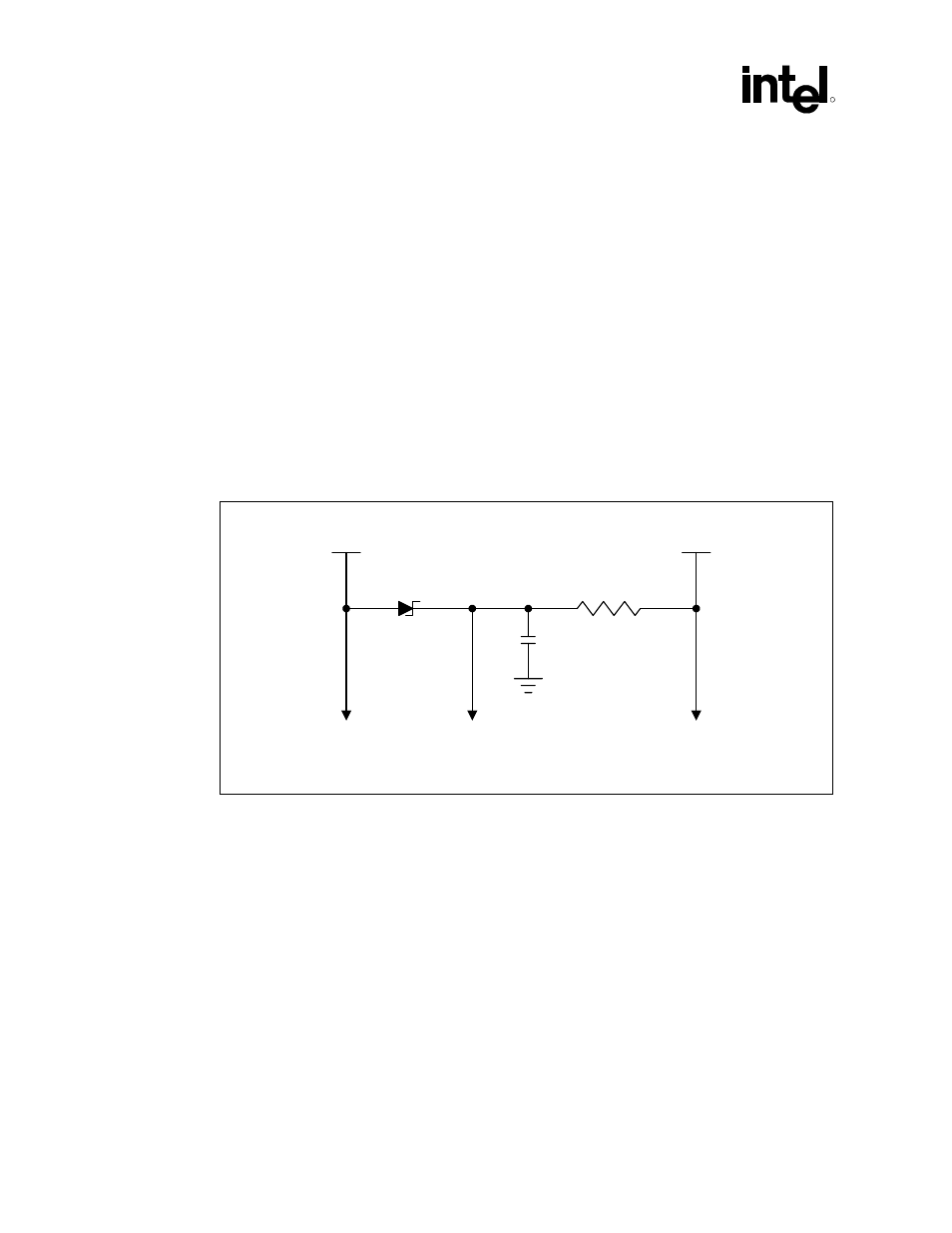

V5REF is the reference voltage for 5V tolerance on inputs to the ICH. V5REF must be powered

up before or simultaneously to VCC3_3. It must also power down after or simultaneous to

VCC3_3. The rule must be followed to ensure the safety of the ICH. If the rule is violated, internal

diodes will attempt to draw power sufficient to damage the diodes from the VCC3_3 rail.

Figure 78 shows a sample implementation of how to satisfy the V5REF/3.3V sequencing rule.

This rule also applies to the stand-by rails, but in most platforms, the VCCSus3_3 rail is derived

from the VCCSus5 and therefore, the VCCSus3_3 rail will always come up after the VCCSus5

rail. As a result, V5REF_Sus will always be powered up before VCCSus3_3. In platforms that do

not derive the VCCSus3_3 rail from the VCCSus5 rail, this rule must be comprehended in the

platform design. As an additional consideration, during suspend the only signals that are 5V

tolerant are USBOC. If these signals are not needed during suspend, V5REF_Sus can be hooked to

the VCCSus3_3 rail.

Figure 78. 3.3V/V5REF Sequencing Circuitry

Vcc Supply

(3.3V)

5V Supply

To System

V

REF

To System

1 K

Ω

1.0 uF

vref_circuit