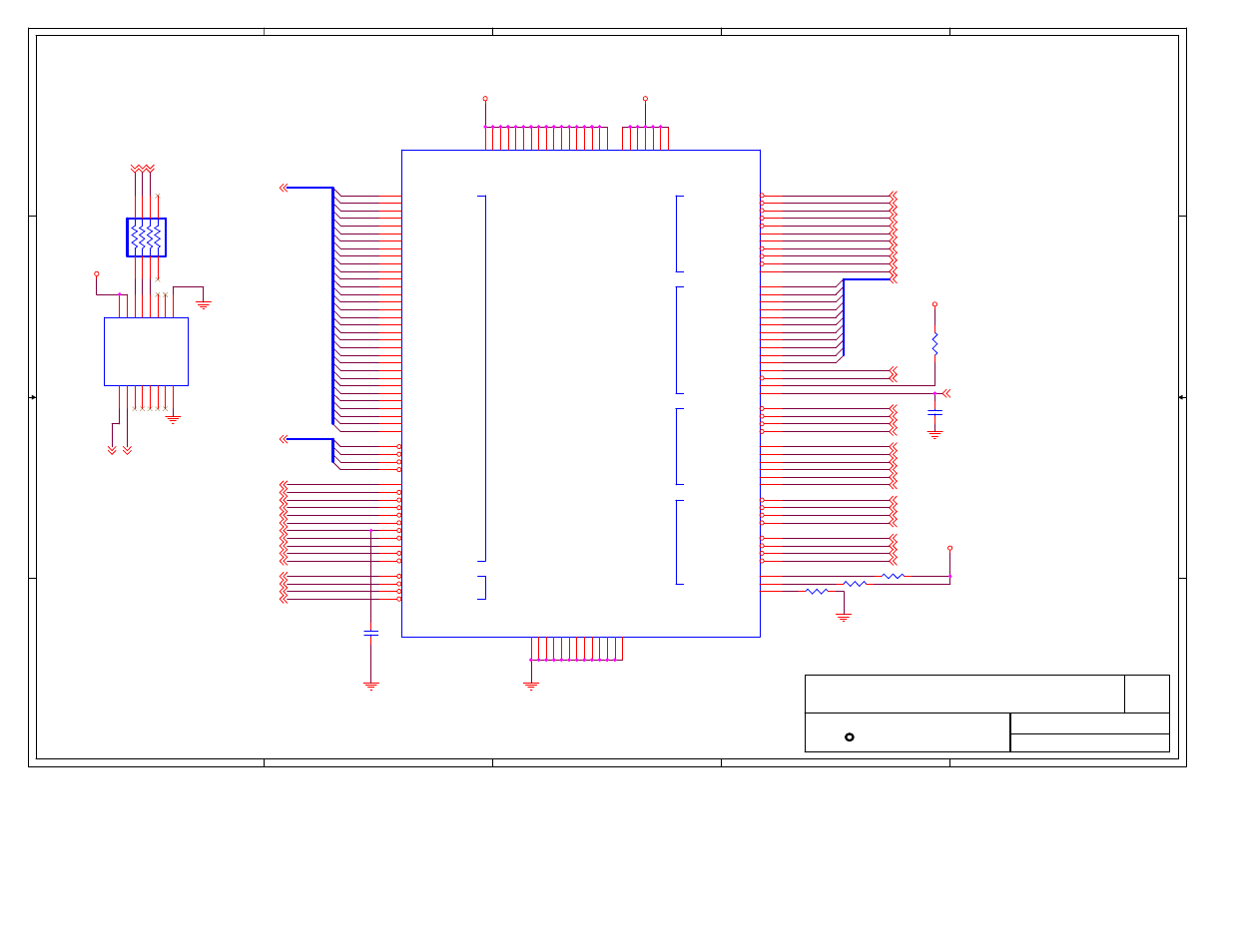

Ich, part 1, Intel, Adm1023 – Intel 815 User Manual

Page 185

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

Place R178

as close as

possible to

ICH

Place C291

as close as

possible to

ICH

Don't Stuff R173

For Test/Debug

No Pop

ICH, PART 1

INTEL(R) 82815 CHIPSET CUSTOMER REFERENCE BOARD

ICH, PART 1

40

1.0

3-26-01

12

Platform Apps Engineering

1900 Prairie City Road

Folsom, CA 95630

REV.

R

Last Revision Date:

Sheet:

of

Title:

intel

AD3

AD4

AD15

FRAME#

HL4

HL9

HLSTB

PREQ#1

C_BE#1

GNT#B/GPIO17

HL10

PIRQ#A

C_BE#[3:0]

AD1

AD5

AD9

AD17

AD26

A20GATE

HL0

APICD0

AD12

AD16

AD20

AD31

PCPCI_REQ#A

PIRQ#B

IRQ15

APICCLK_ICH

APICD1

AD0

AD21

FERR#

PIRQ#D

AD6

AD7

AD24

AD28

RCIN#

HL2

HL3

PREQ#2

PGNT#2

AD22

AD30

PCI_PME#

REQ#B/GPIO1

HL8

AD14

DEVSEL#

PAR

INIT#

HL6

IRQ14

PGNT#1

AD8

IRDY#

STOP#

HLSTB#

HL[10:0]

AD19

AD27

C_BE#2

C_BE#3

PCIRST#

PCPCI_GNT#A

PGNT#0

AD2

AD18

TRDY#

PLOCK#

AD23

AD29

SMI#

STPCLK#

HL5

PREQ#3

AD10

CPUSLP#

HL1

SERIRQ

PCLK_0/ICH

A20M#

HL7

PIRQ#C

PGNT#3

AD11

C_BE#0

IGNNE#

INTR

NMI

PREQ#0

AD[31:0]

AD13

AD25

SERR#

IHCOMP_PU

RESV0PU

RESV1PU

RESV2RD

HUBREF

ALERT

SCLK#

SDATA

AD[31:0]

16,17,29

C_BE#[3:0]

16,17,29

PCLK_0/ICH

5

FRAME#

16,17,29,36

DEVSEL#

16,17,29,36

IRDY#

16,17,29,36

TRDY#

16,17,29,36

STOP#

16,17,29,36

PCIRST#

6,9,14,15,16,17,18,19,24,29

PLOCK#

16,17,36

PAR

16,17,29

SERR#

16,17,29,36

PCI_PME#

9,16,17,29

PCPCI_REQ#A

17,36

PCPCI_GNT#A

17

REQ#B/GPIO1

36

GNT#B/GPIO17

36

FERR#

4,36

IGNNE#

4,36

INIT#

4,14,36

INTR

4,36

NMI

4,36

SMI#

4,36

STPCLK#

4,36

RCIN#

15,36

A20GATE

15,36

HL[10:0]

8,39

HLSTB

8,39

HLSTB#

8,39

PIRQ#A

9,16,17,29,36

PIRQ#B

9,16,17,36

PIRQ#C

16,17,36

PIRQ#D

16,17,36

IRQ14

18,36

IRQ15

18,36

APICCLK_ICH

5

APICD1

4,36

APICD0

4,36

SERIRQ

15,17,36

PREQ#0

36

PREQ#1

16,36

PREQ#2

17,36

PREQ#3

29,36

PGNT#0

36

CPUSLP#

4,36

A20M#

4,36

PGNT#1

16,36

PGNT#2

17,36

PGNT#3

29,36

HUBREF

7,8,39

THERMDN

4

SMBDATA

10,11,13,25,30,36

THERMDP

4

SMBCLK

10,11,13,25,30,36

THERM#

13,36

VCC1_8

VCC3_3

VCC1_8

VCC3_3

VCC3_3

R178

40 1%

1

2

C291

0.1UF

1

2

PCI

PCI

CPU

HUB I/F

PC/PCI

IRQ

INTEL 82801AA

PART 1

82815 ICH

U21-1

R2

G3

H8

J8

K8

H9

J9

K9

H10

J10

K10

G14

K15

E3

G5

P6

T7

U10

R13

T16

M14

C11

C8

A5

E6

E5

D16

N5

N13

E13

G13

H14

K14

G15

L15

H16

J16

F13

E12

F15

B17

E15

E14

B16

F14

A17

A15

B15

D17

E17

F17

G16

J15

K16

K17

L17

H15

J17

J14

G17

H17

M17

J13

D10

A10

B10

C10

P11

N14

C16

C17

E16

R4

A14

B13

B12

D12

A13

C13

A12

C12

A11

B11

F16

G2

G4

F2

F3

F4

F5

E1

E2

D1

D3

E4

C2

C1

B1

D4

C3

A4

B4

C5

C6

B5

E7

A6

B6

D7

B8

A7

A8

B7

C9

D8

C7

D2

B2

A3

D6

C14

B3

D9

A2

C4

D5

J5

B9

A9

A1

K1

N6

P5

P4

R5

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VCC3_3_1

VCC3_3_2

VCC3_3_3

VCC3_3_4

VCC3_3_5

VCC3_3_6

VCC3_3_7

VCC3_3_8

VCC3_3_9

VCC3_3_10

VCC3_3_11

VCC3_3_12

VCC3_3_13

VCC3_3_14

VCC3_3_15

VCC3_3_16

VCC3_3_17

VCC1_8_1

VCC1_8_2

VCC1_8_3

VCC1_8_4

VCC1_8_5

VCC1_8_6

VCC1_8_7

A20M#

CPUSLP#

FERR#

IGNNE#

INIT#

INTR

NMI

SMI#

STPCLK#

RCIN#

A20GATE

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HLSTB

HLSTB#

HCOMP

HUBREF

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

IRQ14

IRQ15

APICCLK

APICD1

APICD0

SERIRQ

REQ#0

REQ#1

REQ#2

REQ#3

GNT#0

GNT#1

GNT#2

GNT#3

GNT4#

REQ4#

HL11

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

PCICLK

FRAME#

DEVSEL#

IRDY#

TRDY#

STOP#

PCIRST#

PLOCK#

PAR

SERR#

PME#

REQ#A/GPIO0

GNT#A/GPIO16

REQ#B/GPIO1/REQ5#

GNT#B/GPIO17/GNT5#

R213

8.2K

1

2

R173

0K

1

2

R212

8.2K

1

2

C312

10PF

1

2

ADM1023

U1

2

15

14

12

11

10

6

8

3

4

13

1

16

5

9

7

VDD

STBY#

SCLK#

SDATA

ALERT

ADD0

ADD1

VSS1

D+

D-

NC

TEST0

TEST1

NC0

NC1

VSS0

RP10

0K

1

2

3

4

5

6

7

8