Intel 815 User Manual

Page 30

Universal Socket 370 Design

R

30

Intel

®

815 Chipset Platform Design Guide

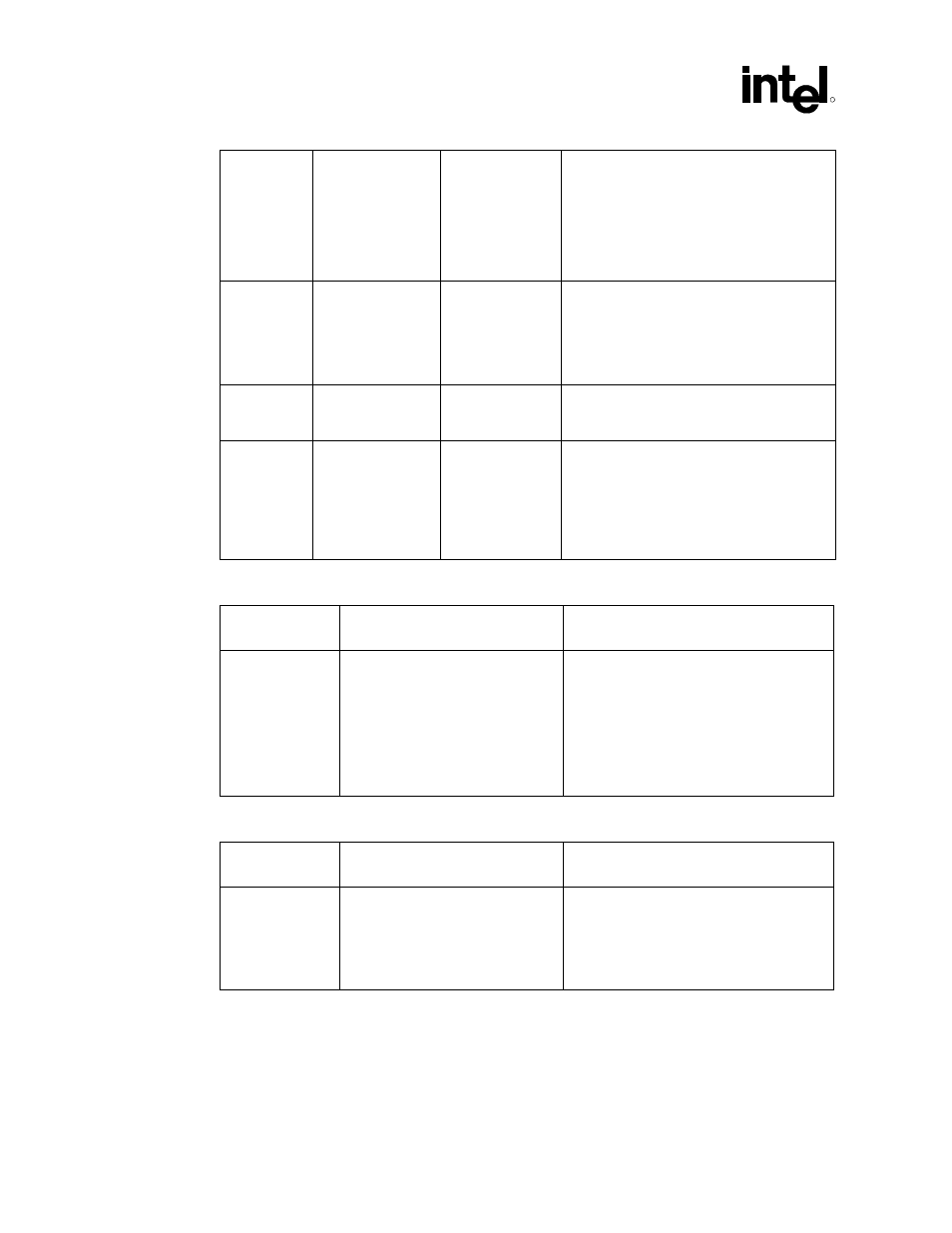

Signal

Name or

Pin

Number

Function In

Intel

®

Pentium

®

III Processor

(CPUID=068xh)

and Intel

®

Celeron™

Processor

(CPUID=068xh)

Function In

Future

0.13 Micron

Socket 370

Processors

Implementation for

Universal Socket 370 Design

PWRGOOD

Requires 2.5V

Requires 1.8V

Addition of resistor-divider network to provide

2.1V, which will satisfy voltage tolerance

requirements of the Pentium III processor

(CPUID=068xh) and Celeron processor

(CPUID=068xh) as well as future 0.13 micron

socket 370 processors.

VTT

Requires 1.5V

Requires 1.25V

Modification to VTT generation circuit to

switch between 1.5V or 1.25V, controlled by

processor identification signal.

VTTPWRGD

Not used

Input signal to

future

0.13 micron

socket 370

processors to

indicate that VID

signals are stable

Addition of VTTPWRGD generation circuit.

Table 2. GMCH Considerations for Universal Socket 370 Design

Pin

Name/Number

Issue Implementation

For

Universal Socket 370 Design

SMAA12

New strap required for determining

Pentium

®

III Processor

(CPUID=068xh) and Intel

®

Celeron™

Processor (CPUID=068xh)

or

Future 0.13 micron socket 370

processors

Addition of FET switch controlled by

processor identification signal.

Table 3. ICH Considerations for Universal Socket 370 Design

Signal Issue

Implementation

For

Universal Socket 370 Design

PWROK

GMCH and Intel

®

CK-815 must not

sample BSEL[1:0] until VTTPWRGD

asserted. ICH must not initialize

before Intel CK-815 clocks stabilize

Addition of circuitry to have VTTPWRGD

gate PWROK from power supply to ICH. The

ICH will hold the GMCH in reset until

VTTPWRGD asserted plus 20 ms time delay

to allow Intel CK-815 clocks to stabilize.