Transmit side timing figure 37-11 – Maxim Integrated DS21Q55 User Manual

Page 244

Product Preview

DS21Q55

244 of 248

012103

Please contact

or search

http://www.maxim-ic.com

for updated

information.

4) TSYSCLK = 8.192MHz.

5) TSYSCLK = 16.384MHz

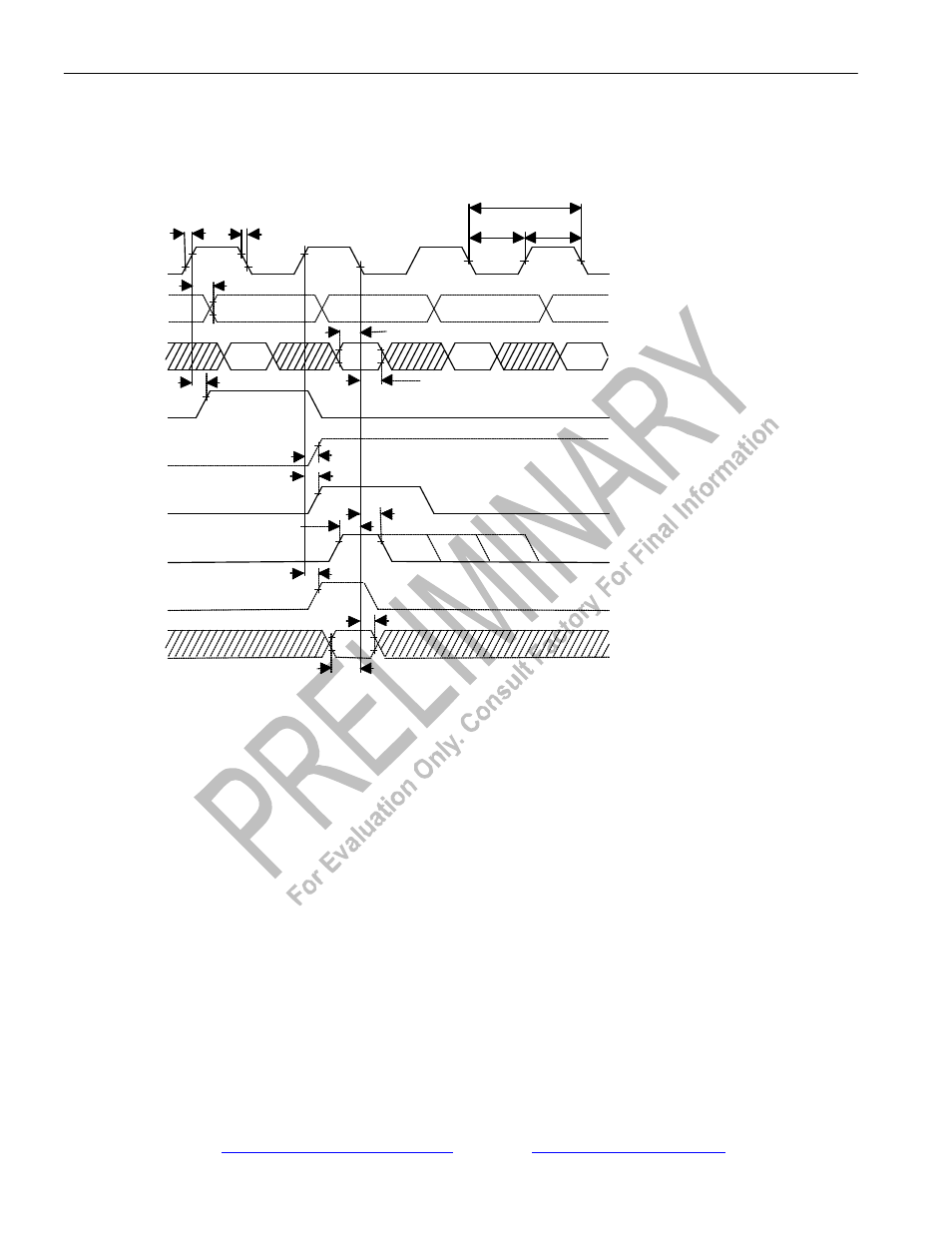

TRANSMIT SIDE TIMING Figure 37-11

4) TCHCLK and TCHBLK are synchronous with TCLK when the transmit-side elastic store is disabled.

NOTES:

1) TSYNC is in the output mode (TCR2.2 = 1).

2) TSYNC is in the input mode (TCR2.2 = 0).

3) TSER is sampled on the falling edge of TCLK when the transmit-side elastic store is disabled.

5) TLINK is only sampled during F-bit locations.

6) No relationship between TCHCLK and TCHBLK and the other signals is implied.

t

F

t

R

1

TCLK

TSER / TSIG /

TDATA

TCHCLK

t

t

CL

t

CH

CP

TSYNC

TSYNC

TLINK

TLCLK

TCHBLK

t

D2

t

D2

t

D2

t

t

t

t

t

t

HD

SU

D2

SU

HD

D1

t

HD

2

5

TESO

t

SU