Maxim Integrated DS21Q55 User Manual

Page 180

Product Preview

DS21Q55

180 of 248

012103

Please contact

or search

http://www.maxim-ic.com

for updated

information.

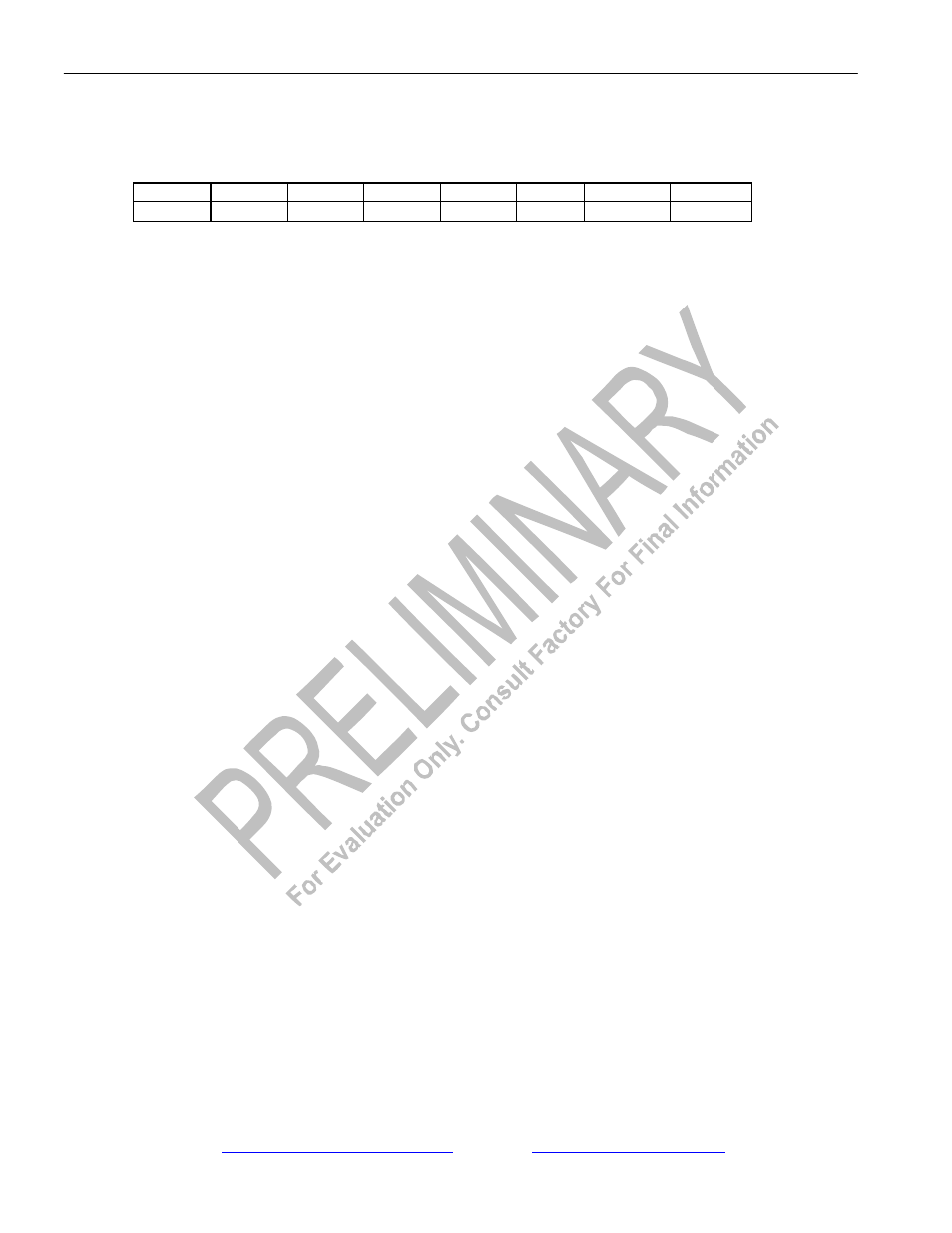

Register Name:

BIC

Register Description:

BER T Interface Control Register

Register Address:

EAh

Bit #

7

6

5

4

3

2

1

0

Name

-

RFUS

-

TBAT

TFUS

-

BERTDIR

BERTEN

Default

0

0

0

0

0

0

0

0

Bit 0/BERT Enable (BERTEN).

0 = BERT disabled

1 = BERT enabled

Bit 1/BERT Direction (BERTDIR).

0 = network

1 = system

Bit 2/Unused, must be set to zero for proper operation.

Bit 3/Transmit Framed/Unframed Select (TFUS). For T1 mode only.

0 = BERT will not source data into the F-bit position (framed)

1 = BERT will source data into the F-bit position (unframed)

Bit 4/Transmit Byte Align Toggle (TBAT). A zero-to-one transition will force the BERT to byte align its pattern with the

transmit formatter. This bit must be transitioned in order to byte-align the Daly Pattern.

Bit 5/Unused, must be set to zero for proper operation.

Bit 6/Receive Framed/Unframed Select (RFUS). For T1 mode only.

0 = BERT will not sample data from the F-bit position (framed)

1 = BERT will sample data from the F-bit position (unframed)

Bit 7/Unused, must be set to zero for proper operation.