Maxim Integrated DS21Q55 User Manual

Page 217

Product Preview

DS21Q55

217 of 248

012103

Please contact

or search

http://www.maxim-ic.com

for updated

information.

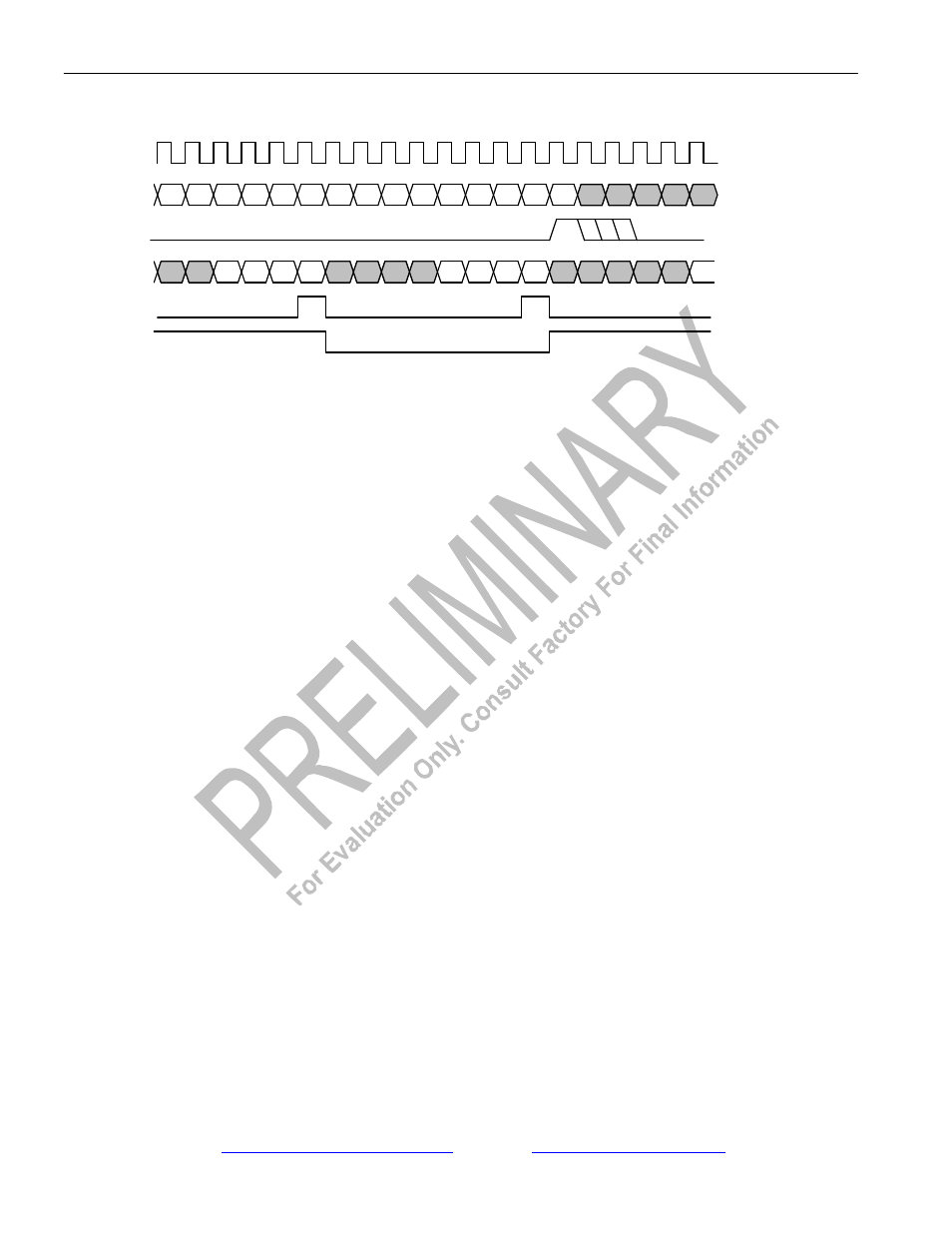

TRANSMIT SIDE 2.048MHz BOUNDARY TIMING (With Elastic Store Enabled)

Figure 35-11

NOTES:

1) TSER data in channels 1, 5, 9, 13, 17, 21, 25, and 29 is ignored.

2) TCHBLK is programmed to block channel 31 (if the TPCSI bit is set, then the signaling data at TSIG

will be ignored).

3) TCHBLK is forced to one in the same channels as TSER is ignored (Note 1).

4) The F-bit position for the T1 frame is sampled and passed through the transmit side elastic store into

the MSB bit position of channel 1. (Normally the transmit side formatter overwrites the F-bit position

unless the formatter is programmed to pass-through the F-bit position).

LSB

F

LSB MSB

CHANNEL 1

CHANNEL 32

A

B

C/A D/B

A

B

C/A

D/B

TSYSCLK

TSER

TSSYNC

TSIG

TCHCLK

TCHBLK

CHANNEL 31

A

CHANNEL 31

CHANNEL 32

CHANNEL 1

1

4

2,3