Maxim Integrated DS21Q55 User Manual

Page 108

Product Preview

DS21Q55

108 of 248

012103

Please contact

or search

http://www.maxim-ic.com

for updated

information.

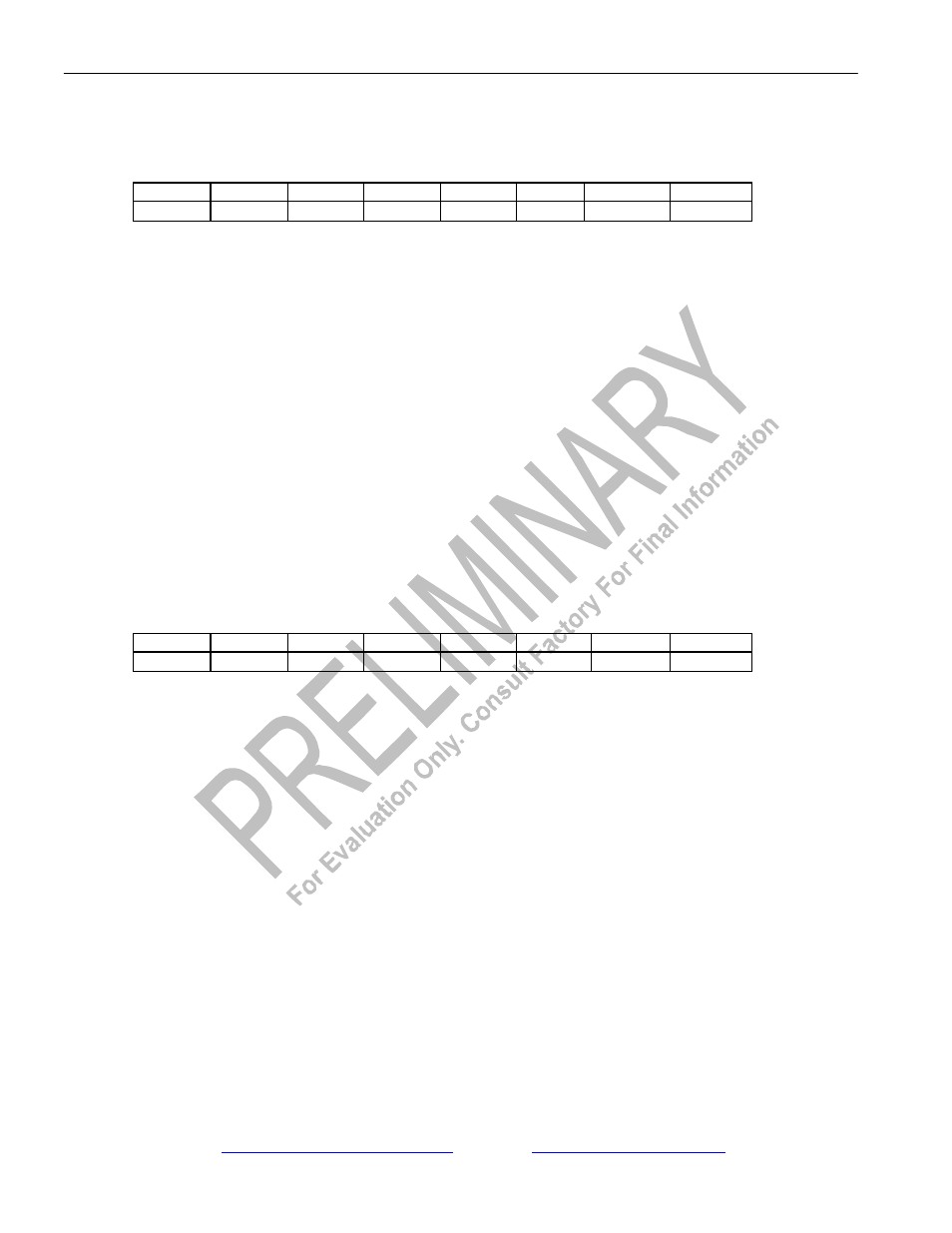

Register Name:

SR5

Register Description:

Status Register 5

Register Address:

1Eh

Bit #

7

6

5

4

3

2

1

0

Name

-

-

TESF

TESEM

TSLIP

RESF

RESEM

RSLIP

Default

0

0

0

0

0

0

0

0

Bit 0/Receive Elastic Store Slip Occurrence Event (RSLIP). Set when the receive elastic store has either repeated or deleted

a frame.

Bit 1/Receive Elastic Store Empty Event (RESEM). Set when the receive elastic store buffer empties and a frame is

repeated.

Bit 2/Receive Elastic Store Full Event (RESF). Set when the receive elastic store buffer fills and a frame is deleted.

Bit 3/Transmit Elastic Store Slip Occurrence Event (TSLIP). Set when the transmit elastic store has either repeated or

deleted a frame.

Bit 4/Transmit Elastic Store Empty Event (TESEM). Set when the transmit elastic store buffer empties and a frame is

repeated.

Bit 5/Transmit Elastic Store Full Event (TESF). Set when the transmit elastic store buffer fills and a frame is deleted.

Register Name:

IMR5

Register Description:

Interrupt Mask Register 5

Register Address:

1Fh

Bit #

7

6

5

4

3

2

1

0

Name

-

-

TESF

TESEM

TSLIP

RESF

RESEM

RSLIP

Default

0

0

0

0

0

0

0

0

Bit 0/Receive Elastic Store Slip Occurrence Event (RSLIP).

0 = interrupt masked

1 = interrupt enabled

Bit 1/Receive Elastic Store Empty Event (RESEM).

0 = interrupt masked

1 = interrupt enabled

Bit 2/Receive Elastic Store Full Event (RESF).

0 = interrupt masked

1 = interrupt enabled

Bit 3/Transmit Elastic Store Slip Occurrence Event (TSLIP).

0 = interrupt masked

1 = interrupt enabled

Bit 4/Transmit Elastic Store Empty Event (TESEM).

0 = interrupt masked

1 = interrupt enabled

Bit 5/Transmit Elastic Store Full Event (TESF).

0 = interrupt masked

1 = interrupt enabled